PAPER Special Section on Solid-State Circuit Design—Architecture, Circuit, Device and Design Methodology

# A Second-Order All-Digital TDC with Low-Jitter Frequency Shift Oscillators and Dynamic Flipflops\*

Toshihiro KONISHI<sup>†a)</sup>, Student Member, Keisuke OKUNO<sup>†</sup>, Nonmember, Shintaro IZUMI<sup>†</sup>, Masahiko YOSHIMOTO<sup>†</sup>, and Hiroshi KAWAGUCHI<sup>†</sup>, Members

**SUMMARY** We present a small-area second-order all-digital time-to-digital converter (TDC) with two frequency shift oscillators (FSOs) comprising inverter chains and dynamic flipflops featuring low jitter. The proposed FSOs can maintain their phase states through continuous oscillation, unlike conventional gated ring oscillators (GROs) that are affected by transistor leakage. Our proposed FSOTDC is more robust and is eligible for all-digital TDC architectures in recent leaky processes. Low-jitter dynamic flipflops are adopted as a quantization noise propagator (QNP). A frequency mismatch occurring between the two FSOs can be canceled out using a least mean squares (LMS) filter so that second-order noise shaping is possible. In a standard 65-nm CMOS process, an SNDR of 61 dB is achievable at an input bandwidth of 500 kHz and a sampling rate of 16 MHz, where the respective area and power are 700 μm² and 281 μW. **key words:** ADC, TDC, oscillator, digital circuit, adaptive LMS filtering

#### 1. Introduction

To produce competitive information and communication equipment, designing high-performance and low-cost chips at low power is needed. Scaling in process technology has enabled miniaturization of transistors. Consequently, the number of transistors can be increased. Functionality in a digital system has developed rapidly at low cost. The low-power feature is also achieved by reducing the supply voltage.

For analog circuits, however, it is difficult to benefit from scaling. Operating at low supply voltage yields a small dynamic range. Linearity becomes degraded, and a gain in an opamp is lowered. To compensate for these disadvantages, transistor sizing and the area of passive components are ever-increasing. Consequently, a mixed-signal chip comprising digital and analog circuitry can achieve neither low cost nor low power in the recent advanced process. An analog-to-digital converter (ADC) is a critical component in mixed-signal circuits, in which opamps and capacitors — particularly in a  $\Delta\Sigma$  ADC — prevent merits derived from scaling.

Several ADCs operating in a time domain have been proposed recently. In the advanced CMOS process, the speed of the transistor will be increasing. It enables TDC

Manuscript received August 7, 2012.

Manuscript revised November 5, 2012.

<sup>†</sup>The authors are with the Department of Computer Science and Systems Engineering, Kobe University, Kobe-shi, 657-8501 Japan.

\*This paper is the extended version of the Symposium on VLSI 2012 [8].

a) E-mail: air@cs28.cs.kobe-u.ac.jp DOI: 10.1587/transele.E96.C.546 to get the more accurate time resolution. A GRO that uses a ring oscillator comprising gated inverters has been studied for use as a TDC [1]. It is noteworthy that this GROTDC has a first-order noise-shaping nature, but only its function as a first-order modulator is described in the literature. Higherorder noise shaping GROTDCs have been reported as presenting the possibility of realizing higher performance [2]. Mandai used GROs and a time difference amplifier as a time residue transmitter [3]. Instead of the GRO, Cao adopted a relaxation oscillator [4]. Gating in the GRO or the relaxation oscillator, however, causes switching noise and transistor leakage at internal nodes storing phase states. The gating transistor must be small to avoid the switching noise, which limits the oscillating frequency and performance. Moreover, the stored phase states are degraded or even lost by the transistor leakage. They are therefore unsuitable for recent leaky processes [5].

In this paper, we propose an opampless second-order MASH TDC topology in the next section. Then, simulation results and measured results with a test chip are described in Sects. 3 and 4, respectively. The final section summarizes this paper.

# 2. Proposed Frequency Shift Oscillator TDC (FSOTDC)

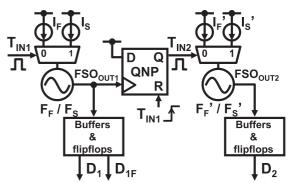

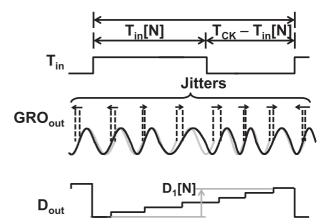

Our proposed FSOTDC architecture is depicted in Fig. 1. No area-consuming capacitor or analog component is used. For that reason, it has process scalability. The FSO on the

FSO: Frequency shift oscillator QNP: Quantization noise propagator

Fig. 1 Proposed second-order frequency-shift-oscillator-based time-todigital converter (FSOTDC) architecture.

first stage outputs a frequency of  $F_{\rm S}$  ( $\approx$  217 MHz: low frequency) or  $F_{\rm F}$  ( $\approx$  557 MHz: high frequency). The FSO layouts of the first and second stages are identical, but their output frequencies differ ( $F_{\rm S} \neq F_{\rm S}$ ',  $F_{\rm F} \neq F_{\rm F}$ ') due to transistor variation. In an extreme case, if all transistors in the first-stage oscillator have a +3 $\sigma$  threshold voltage and those in the second-stage oscillator have a -3 $\sigma$  threshold voltage as local variation (random variation), their output frequencies will change by -15.0%/+15.4%, respectively, even at the typical process corner. This means that the frequency mismatch possibly results in 35.7%. In our proposed architecture, this frequency mismatch can be, however, compensated by a first-order LMS filter.

The FSO presents advantages over a GRO by alleviating problems related to switching noise and transistor leakage [6]. In GRO's gating, the stored phase states are degraded or even lost. The switching noise or transistor leakage will prevent maintenance of its internal state. Unlike the GRO, the FSO does not stop its oscillation or does not maintain its output phase state; use of the FSO eliminates these problems because it continues oscillating. Furthermore, the power supply noise in the FSO is less than that in the GRO because the FSO does not cease oscillating; the fluctuation in switching current is smaller (current fluctuation: FSO =  $I_F - I_S$ , GRO =  $I_F$ ).

Figure 2 depicts a timing diagram of the proposed FSOTDC. Therein, T is a sampling period,  $T_{\rm IN1}$  ( $T_{\rm IN2}$ ) signifies an input pulse width into the first-stage (second-stage) FSO,  $FSO_{\rm OUT1}$  ( $FSO_{\rm OUT2}$ ) stands for its output,  $D_1$  ( $D_2$ ) denotes the number of  $FSO_{\rm OUT1}$  ( $FSO_{\rm OUT2}$ ) oscillations in a sampling period,  $D_{1F}$  denotes the number of oscillations while  $T_{\rm IN1}$  is off, and  $QN_1$  ( $QN_2$ ) represents a quantization noise of  $FSO_{\rm OUT1}$  ( $FSO_{\rm OUT2}$ ). Herein, we define  $\xi$  as a time residue in  $T_{\rm IN1}$ .  $T_{\rm IN1}$  and  $T-T_{\rm IN1}$  are given respectively as (1) and (2).

$$T_{IN1} = \frac{1}{F_S} - \frac{QN_1[n-1] \cdot F_F}{F_S} + \frac{(D_1 - D_{1F})}{F_S} + \xi \quad (1)$$

Fig. 2 FSOTDC timing diagram.

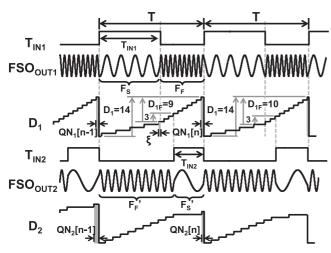

**Fig. 3** (a) Quantization noise propagator (QNP), (b) dynamic D-flipflop, (c) transfer characteristics, and (d) QNP timing diagrams.

$$T - T_{IN1} = \frac{1}{F_E} - \frac{\xi \cdot F_S}{F_E} + \frac{D_{1F}}{F_E} + QN_1[n]$$

(2)

Next,  $D_1$  and  $D_{1F}$ , which are digital values corresponding to  $T_{\text{IN1}}$  and  $T - T_{\text{IN1}}$ , are given respectively as (3) and (4) (where  $F_{\text{F}} \cdot T$  is a constant offset).

$$D_1 = (F_S - F_F) \cdot T_{IN1} + F_F (QN_1[n-1] - QN_1[n]) + F_F \cdot T$$

(3)

$$D_{1F} = -F_F \cdot T_{IN1} + F_F \cdot QN_1[n] + F_F \cdot T \tag{4}$$

In the equations, respective  $QN_1[n-1]$  and  $QN_1[n]$  are quantization noises in the previous and present sampling periods. The QNP detects the third rising-edge of  $FSO_{\rm OUT1}$  (see Fig. 3; because it has three flipflops) when  $T_{\rm IN1}$  is off, and then it outputs  $T_{\rm IN2}$ . In this case,  $T_{\rm IN2}$  is represented as (5).

$$T_{IN2} = QN_1[n] + \frac{D_{1F} - 2}{F_F} \tag{5}$$

By putting (4) in (5), we can obtain (6), from which D2 is given as (7) ( $C_1$  and  $C_2$  are constants).

$$T_{IN2} = -T_{IN1} + 2 \cdot QN_1[n] + C_1 \tag{6}$$

$$D_2 = (F_F' - F_S') \cdot (-T_{IN1} + 2 \cdot QN_1[n]) + F_S' \cdot (QN_2[n-1] - QN_2[n]) + C_2$$

(7)

As depicted in Fig. 3(a), the proposed QNP has three dynamic D-flipflops (DDFFs) to avoid metastability. In the FSOTDC architecture,  $\Delta T$  in Fig. 3(c) might be very small because of continuous oscillation, which might cause metastability in the QNP. The DDFF depicted in Fig. 3(b) is simple and is five times faster than the conventional master-slave flipflop. By connecting the three DDFFs, the metastable period, which worsens stability and linearity, can be minimized to 0.8 ps (Fig. 3(c)). Figure 3(d) illustrates the timing diagrams of the QNP; even if the falling edges of "OUT<sub>1</sub>" and "OUT<sub>2</sub>" at the first and second flipflops get slower by the successive metastabilities, the proposed QNP properly mask the unnecessary delays.

# 3. Simulated Results with Considering Effects of Jitters

Because the simulation of TDC needs high accurate time step, the lower the clock frequency is, the longer the simulation time and the bigger data is needed. Then it is difficult to simulate under the condition of low sampling frequency. In this section, we will discuss the numerical calculation by using MATLAB with considering SPICE simulated results.

Table 1 shows SPICE simulated results of the oscillator, which is used in our proposed TDC. We added the noise sources on power supply lines and set the amplitude of noise to the 10 mVp-p.

# 3.1 Consideration to Timing Jitters

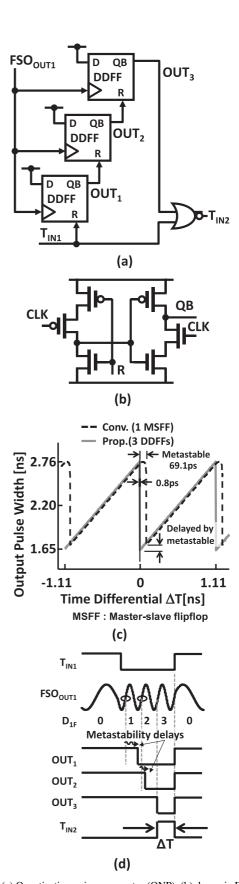

We considered the effect of timing jitter. Actually, when the oscillator is running, there are some jitters as shown in

**Table 1** Simulated data of the oscillator.

| Item                 | $F_{ m S}$ | $F_{ m F}$ |

|----------------------|------------|------------|

| Frequency [GHz]      | 0.217      | 0.557      |

| Period [ns]          | 4.59       | 1.79       |

| Jitter (stddev) [ps] | 3.70       | 1.95       |

| Jitter / Period [%]  | 0.0805     | 0.1085     |

Fig. 4 Timing diagram with considering the effects of the jitters.

Fig. 4. If the jitter exists, the period of FSO<sub>out</sub> may shift.

We define the time difference occurred from the jitters as  $Jitter I_i$  ( $i = 1, 2, 3 ... N j_1$ ) in the slow frequency mode.  $N j_1$  is the total counts of the rising edge during one sample period in the slow frequency mode. And also,  $Jitter 2_i$  ( $i = 1, 2, 3 ... N j_2$ ) are the jitters in the high frequency mode.  $N j_2$  is the total counts of the rising edge during one sample period in the high frequency mode. Then,  $T_{in}$  is expressed as follows:

$$T_{IN1} = \frac{1}{F_S} - \frac{QN_1[n-1] \cdot F_F}{F_S} + \frac{D_1 - D_{1F}}{F_S} + \sum_{i} Jitter 1_i + \xi$$

$$T - T_{IN1} = \frac{1}{F_F} - \frac{\xi \cdot F_S}{F_F} + \frac{D_{1F}}{F_F} + \sum_{i} Jitter 2_i + QN_1[n]$$

(8)

$D_1$  is given as

$$D_{1} = (F_{S} - F_{F}) \cdot T_{IN1} + F_{F} (QN_{1}[n-1] - QN_{1}[n]) + F_{S} \cdot \sum Jitter1_{i} + F_{F} \cdot \sum Jitter2_{i} + F_{F} \cdot T \quad (10)$$

Jitter $l_i$  and Jitter $l_i$  are series of random numbers defined as Gaussian distribution. The average is set to 0. And  $3\sigma$  is set to 0.08–0.11% of the oscillation period. This parameter is based on the SPICE simulation in which 10 mVp-p of white noise is added on the power lines.

# 3.2 Modeling in MATLAB

MATLAB function 1 is the model of the ring oscillator. This function outputs the total counts of the rising edge of the

```

MATLAB function 1 Numerical calculation of the oscil-

lation

function [Do,Po] = OSC(Tin,Pi,Fo,Aj)

Do=0;

Po=Tin*Fo:

N_j = fix(Po+1);

rng('shuffle');

pjitter=Aj.*randn(1,Nj);

Po=Po+Pi;

if Po < 1

Do=0;

else

for j=1:1:Nj

if Po < 1

break

end

Po=Po-(1+pjitter(j));

Do=Do+1;

end

end

```

```

MATLAB function 2 Numerical calculation of the TDC

function [D1,D2,D2d,TDout] = TDC(Tin,T,Nsample)

F1S=217e6;% oscillation frequency during Tin = 'on'

F1F=557e6;% oscillation frequency during Tin = 'off'

F2S=217e6;% oscillation frequency during Tin = 'on'

F2F=557e6;% oscillation frequency during Tin = 'off'

ph1i=0;% initial phase condition of FSO1

ph2i=0;% initial phase condition of FSO2

Aj1=0.08/100;% jitter amplitude of the F_S mode

Aj2=0.11/100;% jitter amplitude of the F_F mode

B1=F1F:

A2=F2S-F2F;

w0 = -A2/B1;

%% Time to digital conversion%%

for i=1:1:Nsample

[D1S(i),Po] = OSC(Tin(i),ph1(i),F1S,Aj1);

[D1F(i),ph1(i+1)] = OSC(T-Tin(i),Po,F1F,Aj2);

rng('shuffle');

Tin2(i)=Tin(i)+(3-Po)/F1F+(0.1e-12).*randn(1);

[D2S(i),Po2] = OSC (Tin2(i),ph2(i),F2S,Aj1);

[D2F(i),ph2(i+1)] = OSC (T-Tin2(i),Po2,F2F,Aj2);

End

%% Noise cancellation%%

D1=D1S+D1F:

D2=D2S+D2F;

D2d=D2-w0*D1F;

for i=1:1:Nsample-1

TDout(i) = -w0*D1(i+1) - (D2d(i+1) - D2d(i));

end

```

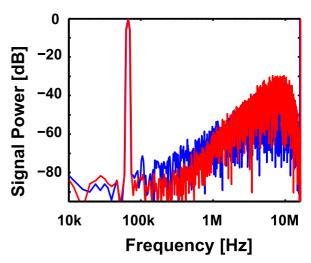

**Fig. 5** Output results of the numerical calculation. CK=16 MHz. Blue and red lines are outputs of the first-order FSOTDC and the second-order FSOTDC respectively.

Table 2

Specifications of the calculated results.

| Item                   | Data |

|------------------------|------|

| Technology (nm)        | 65   |

| Bandwidth (kHz)        | 500  |

| Sampling rate (MS/s)   | 16   |

| First-order SNDR (dB)  | 54   |

| Second-order SNDR (dB) | 63   |

FSO. "Tin" is the width of time-domain input. "Po" is the final phase state of the FSO during the period of "Tin". "Pi" is initial phase state. "Fo" is the frequency of the FSO. "Aj" is the maximum amplitude of the jitters.

MATLAB function 2 is the model of the second-order FSOTDC. And this function outputs the second-order noise shaped output "TDCout" and the first-order noise shaped output "D1". "Tin" is the time series of time-domain input signals. "T" is the frequency of the clock. "Nsample" is the total number of samples. "F1S" means  $F_{\rm S}$ , "F1F" means  $F_{\rm F}$ , "F2S" means  $F_{\rm S}$ , and "F2F" means  $F_{\rm F}$  respectively.

# 3.3 Simulated Results

Figure 5 shows the results of numerical calculations based on the MATLAB models described in the next section (subsection B). The jitters affect the performance of TDC and raise up the noise floors in the low frequency region. Table 2 shows specifications of the calculated results. The input signal frequency is 66.4 kHz, the input signal width is 31.25 ns (signal amplitude is 15.62 ns), and the sampling rate is 16 MHz. The output SNDR of the first-order noise shaping is 54 dB in this case. The output SNDR of the second-order noise shaping is 63 dB, which achieves about a 9-dB improvement in the SNDR.

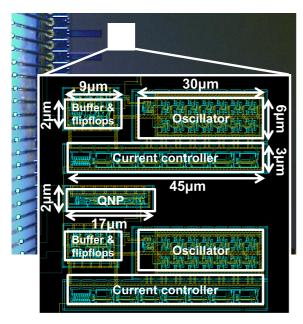

Fig. 6 Chip micrograph.

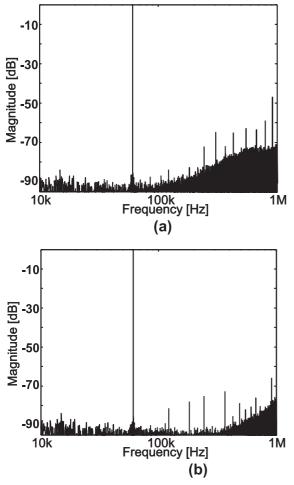

Fig. 7 Output spectra of (a) without LMS and (b) with LMS.

# 4. Measurement Results

A test chip was fabricated using a 65 nm CMOS process (Fig. 6). The TDC core occupies  $700 \,\mu\text{m}^2$  as an active area. The power supply voltage is  $1.2 \,\text{V}$ .

Figures 7(a) and 7(b) show the measured output spectrum of the proposed TDC with and without the LMS filter.

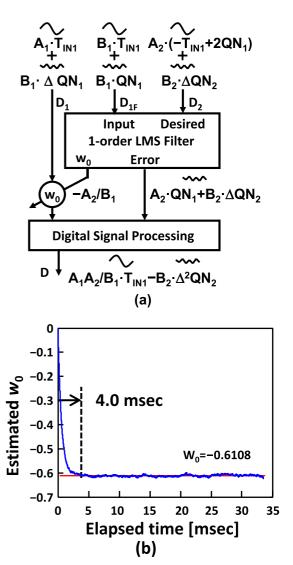

Figure 8(a) presents a conceptual diagram of the first-order LMS filter, which estimates the ratio of the oscillation frequencies (desired coefficient:  $w_0$ ) between the two FSOs adaptively in the manner described above. Figure 8(b) presents results of the estimated coefficients when the sampling rate is 16 MHz, the filter order is one, the internal coefficients are 16bits, and the step size is 0.001. The desired coefficient  $w_0$  can be estimated until 4 milli-seconds. It is apparent that second-order noise shaping is achieved by the LMS filter (see Fig. 7(b)). In the spectra, the input signal frequency is 61 kHz, and the input width is 31.25 ns (the

Fig. 8 (a) Block diagram of LMS for mismatch correction and (b) the elapsed time of the coefficient estimation.

| <b>Table 3</b> Chip character |

|-------------------------------|

|-------------------------------|

| Item                           | Data   |

|--------------------------------|--------|

| Technology (nm)                | 65     |

| Supply voltage (V)             | 1.2    |

| Bandwidth (kHz)                | 500    |

| Sampling rate (MS/s)           | 16     |

| Power (mW)                     | 0.281  |

| SFDR (dB)                      | 72     |

| SNDR (dB)                      | 61     |

| ENOB (bits)                    | 9.8    |

| FoM (fJ/conv.step)             | 308    |

| Active area (mm <sup>2</sup> ) | 0.0007 |

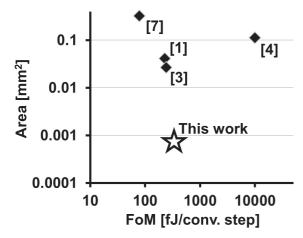

**Fig. 9** Comparison with other state-of-the-art TDCs (a pipeline TDC [7] is added for area comparison).

sampling rate is 16 MHz). The SNDR is 61 dB.

In the test chip, there are some harmonic noises in the outputs of the TDC, which were not found in the SPICE and MATLAB simulations. We suppose that the harmonic noises come from power lines of the oscillators. Except for such harmonic noises, Figs. 5 and 7 exhibit the same noise floor; owing to the second-order noise shaping effect, the both noise floors of the simulation and measurement are decreased by  $-20 \, \text{dB}$  (roughly from  $-70 \, \text{dB}$  to  $-90 \, \text{dB}$ ) in a bandwidth of  $100 \, \text{kHz}$  and  $1 \, \text{MHz}$ . At this point, this measured result matches with the simulated results described in Sect. 3.

The FSOs and QNP consume  $211 \mu W$ . The peripheral buffers and flipflops consume  $70 \mu W$ . The test chip performance is summarized in Table 3. Our TDC is smaller than any other TDCs (see Fig. 9).

# 5. Conclusion

We proposed a 700- $\mu$ m<sup>2</sup>, 61-dB, and 281- $\mu$ W second-order MASH  $\Delta\Sigma$  TDC. In the proposed architecture, analog circuits such as opamps and switched capacitors can be eliminated. The control and calibration of the TDC are imple-

mented with digital circuits, which achieve the low-cost and low-power TDC. The proposed TDC thereby maintains scalability with future advanced processes. Because the proposed architecture is configured by using digital circuits in the standard cell library, the design cost and turn around time (TAT) are reduced as well.

The proposed TDC exploits an oversampling technique. Therefore, by increasing the sampling rate, we can further enhance the quantization accuracy (time resolution) and signal bandwidth. Furthermore, the ENOB can be improved with the third-order or higher MASH topology by connecting multiple stages. As process technology advances, the ring oscillator frequency becomes faster, which is good news for the proposed TDC. Process scaling will back up our proposed TDC architecture in the future.

If we adopt a voltage-to-time converter for our architecture, this TDC can be adopted for a range of applications such as a ubiquitous sensor, in which many ADCs must be implemented on a chip. Therein, one node collects various information through the ADCs; it then forwards it to a base station. Small-area and low-power ADC without opamps or capacitors is useful for the future ubiquitous applications.

# Acknowledgments

This development was performed by the author for STARC as part of the Japanese Ministry of Economy, Trade and Industry sponsored "Silicon Implementation Support Program for Next Generation Semiconductor Circuit Architectures". The chip design was supported by the VLSI Design and Education Center (VDEC) of The University of Tokyo in collaboration with Synopsys Inc., Cadence Design Systems Inc., and Mentor Graphics Corp.

#### References

- M.Z. Straayer and M.H. Perrott, "A multi-path gated ring oscillator TDC with first-order noise shaping," IEEE J. Solid-State Circuits, vol.44, no.4, pp.1089–1098, May 2009.

- [2] T. Konishi, H. Lee, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "A 40-nm 640-μm<sup>2</sup> 45-dB opampless all-digital second-order MASH ΔΣ ADC," IEEE ISCAS, pp.518–521, May 2011.

- [3] S. Mandai and E. Charbon, "A 128-channel, 9 ps column-parallel two-stage TDC based on time difference amplification for timeresolved imaging," Proc. IEEE ESSCIRC, pp.119–122, Sept. 2011.

- [4] Y. Cao, P. Leroux, W. De Cock, and M. Steyaert, "A 1.7 mW 11b 1–1–1 MASH  $\Delta\Sigma$  time-to-digital converter," IEEE ISSCC, pp.480–482, Feb. 2011.

- [5] S. Henzler, Time-to-Digital Converters, Springer, 2010.

- [6] T. Konishi, K. Okuno, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "A 51-dB SNDR DCO-based TDC using two-stage second-order noise shaping," IEEE International Symposium on Circuits and Systems, pp.3170–3173, May 2012.

- [7] Y.-H. Seo, J.-S. Kim, H.-J. Park, and J.-Y. Sim, "A 0.63 ps resolution, 11b pipeline TDC in 0.13 μm CMOS," IEEE Symposium on VLSI Circuits, pp.152–153, June 2011.

- [8] T. Konishi, K. Okuno, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "A 61-dB SNDR 700 \(\mu\mathrm{m}^2\) second-order all-digital TDC with lowjitter frequency shift oscillators and dynamic flipflops," Symposium on VLSI Circuits, pp.190–191, June 2012.

**Toshihiro Konishi** received his B.E. and M.E. degrees from Kobe University, Japan in 2008 and 2010, respectively. He is currently a Ph.D. Candidate at the same university. He engages in low-power digitally controlled oscillator, analog to digital converter, time to digital converter designs, digitally assisted analog and digital signal processing.

**Keisuke Okuno** received a B.E. degree in Computer and Systems Engineering from Kobe University, Hyogo, Japan, in 2011. Currently, he is a master course student at Kobe University. His current research interests include digital signal processing and adaptive filters.

Shintaro Izumi received his B.Eng. and M.Eng. degrees in Computer Science and Systems Engineering from Kobe University, Hyogo, Japan, in 2007 and 2008, respectively. He received his Ph.D. degree in Engineering from Kobe University in 2011. He was a JSPS research fellow at Kobe University from 2009 to 2011. Since 2011, he has been an Assistant Professor in the Organization of Advanced Science and Technology at Kobe University. His current research interests include biomedical signal

processing, communication protocols, low-power VLSI design, and sensor networks. He is a member of the IEEE and IPSJ.

Masahiko Yoshimoto joined the LSI Laboratory, Mitsubishi Electric Corporation, Itami, Japan, in 1977. From 1978 to1983 he had been engaged in the design of NMOS and CMOS static RAM. Since 1984 he had been involved in the research and development of multimedia ULSI systems. He earned a Ph.D. degree in Electrical Engineering from Nagoya University, Nagoya, Japan in 1998. Since 2000, he had been a professor of Dept. of Electrical & Electronic System Engineering in Kanazawa Univer-

sity, Japan. Since 2004, he has been a professor of Dept. of Computer and Systems Engineering in Kobe University, Japan. His current activity is focused on the research and development of an ultra-low power multimedia and ubiquitous media VLSI systems and a dependable SRAM circuit. He holds on 70 registered patents. He has served on the program committee of the IEEE International Solid State Circuit Conference from 1991 to 1993. Also he served as Guest Editor for special issues on Low-Power System LSI, IP and Related Technologies of IEICE Transactions in 2004. He was a chair of IEEE SSCS (Solid State Circuits Society) Kansai Chapter from 2009 to 2010. He is also a chair of The IEICE Electronics Society Technical Committee on Integrated Circuits and Devices from 2011–2012. He received the R&D100 awards from the R&D magazine for the development of the DISP and the development of the real-time MPEG2 video encoder chipset in 1990 and 1996, respectively. He also received 21st TELECOM System Technology Award in 2006.

Hiroshi Kawaguchi received B.Eng. and M.Eng. degrees in electronic engineering from Chiba University, Chiba, Japan, in 1991 and 1993, respectively, and earned a Ph.D. degree in electronic engineering from The University of Tokyo, Tokyo, Japan, in 2006. He joined Konami Corporation, Kobe, Japan, in 1993, where he developed arcade entertainment systems. He moved to The Institute of Industrial Science, The University of Tokyo, as a Technical Associate in 1996, and was appointed as a

Research Associate in 2003. In 2005, he moved to Kobe University, Kobe, Japan. Since 2007, he has been an Associate Professor with The Department of Information Science at that university. He is also a Collaborative Researcher with The Institute of Industrial Science, The University of Tokyo. His current research interests include low-voltage SRAM, RF circuits, and ubiquitous sensor networks. Dr. Kawaguchi was a recipient of the IEEE ISSCC 2004 Takuo Sugano Outstanding Paper Award and the IEEE Kansai Section 2006 Gold Award. He has served as a Design and Implementation of Signal Processing Systems (DISPS) Technical Committee Member for IEEE Signal Processing Society, as a Program Committee Member for IEEE Custom Integrated Circuits Conference (CICC) and IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips), and as an Associate Editor of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and IPSJ Transactions on System LSI Design Methodology (TSLDM). He is a member of the IEEE, ACM, and IPSJ.