# on Fundamentals of Electronics, Communications and Computer Sciences

VOL. E98-A NO. 7 JULY 2015

The usage of this PDF file must comply with the IEICE Provisions on Copyright.

The author(s) can distribute this PDF file for research and educational (nonprofit) purposes only.

Distribution by anyone other than the author(s) is prohibited.

PAPER Special Section on Design Methodologies for System on a Chip

# Low-Jitter Design for Second-Order Time-to-Digital Converter Using Frequency Shift Oscillators\*

Keisuke OKUNO<sup>†a)</sup>, Student Member, Toshihiro KONISHI<sup>†</sup>, Nonmember, Shintaro IZUMI<sup>†</sup>, Masahiko YOSHIMOTO<sup>†</sup>, and Hiroshi KAWAGUCHI<sup>†</sup>, Members

**SUMMARY** We present a low-jitter design for a 10-bit second-order frequency shift oscillator time-to-digital converter (FSOTDC). As described herein, we analyze the relation between performance and FSOTDC parameters and provide insight to support the design of the FSOTDC. Results show that an oscillator jitter limits the FSOTDC resolution, particularly during the first stage. To estimate and design an FSOTDC, the frequency shift oscillator requires an inverter of a certain size. In a standard 65-nm CMOS process, an SNDR of 64 dB is achievable at an input signal frequency of 10 kHz and a sampling clock of 2 MHz. Measurements of the test chip confirmed that the measurements match the analyses.

key words: TDC, FSO, jitter, design methodology

#### 1. Introduction

Time-to-digital converters (TDCs), which digitalize a time interval, are used in all-digital phase locked loops (AD-PLLs) and analog-to-digital converters (ADCs). The timedomain ADC using the TDC can be configured using digital circuits. Therefore, they can be extended easily to advanced CMOS processes. The minimum time resolution of the state-of-the art TDC is 180 fs [2]. The TDC, which can be realized in a small area and at low cost, requires an external circuit to convert a signal (with analog voltage) to a time-domain signal, although voltage-to-time converters reportedly achieve good linearity [1]. The combination of the TDC and voltage-to-time converter can produce a highperformance ADC that uses a small area. To obtain the small area and high resolution, the proposed TDC consists of a pair of inverter rings as oscillators. The oscillators are called frequency-shift oscillators that output either low frequency or high frequency on demand [3]. The second-order frequency shift oscillator TDC (FSOTDC) achieves smaller area with simple architecture.

In the next section, to estimate an FSOTDC resolution, we describe analysis of the factors affecting the FSOTDC performance. Then, simulation results derived from the analyses and measurement results of a test chip are described in Sect. 3. The final section summarizes this paper.

Manuscript received September 17, 2014.

Manuscript revised January 12, 2015.

a) E-mail: okuno@cs28.cs.kobe-u.ac.jp DOI: 10.1587/transfun.E98.A.1475

# 2. Analyses of Second-Order FSOTDC

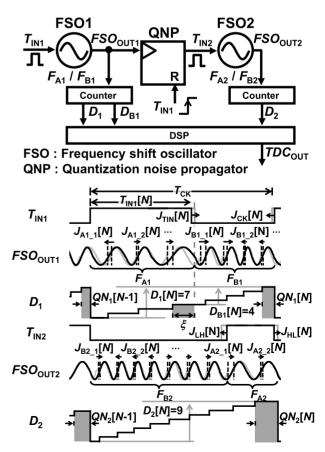

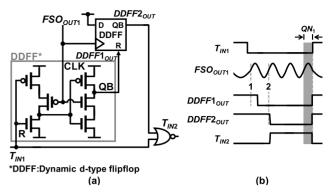

Figure 1 portrays the architecture and the timing diagram of the second-order  $\Delta\Sigma$  FSOTDC. The first-stage FSOTDC converts an input time at the N-th sample  $(T_{\text{INI}}[N])$  to a digital value  $(D_1[N])$  using an FSO, which oscillates at a low frequency or high frequency  $(F_{\text{A1}} \text{ or } F_{\text{B1}})$  depending on  $T_{\text{INI}}[N]$  ( $F_{\text{A1}}$  when  $T_{\text{IN1}}[N]$  = "High";  $F_{\text{B1}}$  when  $T_{\text{IN1}}[N]$  = "Low"). Consequently,  $D_1[N]$  signifies the total oscillation count during a sampling period  $(T_{\text{CK}})$ .  $J_{\text{CK}}[N]$  and  $J_{\text{TIN}}[N]$  are jitters in a clock period and an input signal.  $D_{\text{B1}}[N]$  is a digital value corresponding to  $T_{\text{CK}} - T_{\text{IN1}}[N]$ .  $J_{\text{A1}}[N]$  ( $X_{\text{IN}}[N]$ ) and  $J_{\text{B1}}[N]$  ( $X_{\text{IN}}[N]$ ) represent timing jitters at the respective oscillation frequencies of  $F_{\text{A1}}$  and  $F_{\text{B1}}$

Fig. 1 FSOTDC architecture and timing diagrams.

<sup>&</sup>lt;sup>†</sup>The authors are with the Department of Computer Science and Systems Engineering, Kobe University, Kobe-shi, 657-8501 Japan.

<sup>\*</sup>This is an extended version of NEWCAS 2012 [5].

at the *N*-th sample.  $\Sigma J_{A1}[N]$  and  $\Sigma J_{B1}[N]$  respectively denote the sums of  $J_{A1}[N]$  and  $J_{B1}[N]$ . When the jitters are considered,  $D_1[N]$  can be derived from [3] as

$$D_{1}[N] = (F_{A1} - F_{B1}) \cdot T_{IN1}[N] - F_{B1} \cdot \Delta Q N_{1} + F_{B1} \cdot T_{CK}$$

$$+ F_{A1} \cdot \sum_{A_{1}[N]} J_{A1}[N] + F_{B1} \cdot \sum_{A_{1}[N]} J_{B1}[N]$$

$$+ J_{TIN}[N] + J_{CK}[N], \qquad (1)$$

where  $\Delta$  is the difference from the previous amount, that is,  $\Delta QN_1$  is  $QN_1[N] - QN_1[N-1]$ . Actually, (1) shows that the first-stage FSOTDC indeed achieves first-order noise shaping if no jitter occurs. To extend it to the second-order TDC, the FSOTDC has a quantization noise propagator (QNP) between the first and second stages, which propagates a quantization noise. The QNP output  $(T_{\text{IN2}}[N])$  is another input for the second-stage FSO, which includes  $QN_1[N]$ .  $T_{\text{IN2}}[N]$ , which has timing jitters  $J_{\text{LH}}[N]$  and  $J_{\text{HL}}[N]$ , is defined as shown below.

$$T_{\text{IN2}}[N] = \frac{D_{\text{B1}}[N] - 3}{F_{\text{B1}}} + QN_1[N] + J_{\text{LH}}[N] + J_{\text{HL}}[N]. \tag{2}$$

In the second stage, the second-stage FSO oscillates at  $F_{\rm A2}$  or  $F_{\rm B2}$ .  $J_{\rm A2\_X}[N]$  and  $J_{\rm B2\_x}[N]$  represent timing jitters as well. The second-stage digital output,  $D_2[{\rm N}]$ , is represented as

$$D_{2}[N] = (F_{A2} - F_{B2}) \cdot T_{IN2}[N] - F_{A2} \cdot \Delta Q N_{2} + F_{B2} \cdot T_{CK}$$

$$+ F_{A2} \cdot \sum_{A_{2}} J_{A2}[N] + F_{B2} \cdot \sum_{A_{2}} J_{B2}[N]$$

$$+ J_{LH}[N] + J_{HL}[N].$$

(3)

Eventually, from (1), (2), and (3), the final output,  $TDC_{OUT}[N]$ , including the second-order noise shaping, can be expressed as shown below.

$$TDC_{\text{OUT}}[N] = \frac{A_2}{F_{\text{B1}}} \cdot D_1[N] + \Delta \left( D_2[N] - \frac{A_2}{F_{\text{B1}}} \cdot D_{\text{B1}}[N] \right)$$

$$= \frac{A_2}{F_{\text{B1}}} \left( A_1 \cdot T_{\text{IN1}}[N] + F_{\text{A1}} \cdot \sum J_{\text{A1}}[N] + F_{\text{B1}} \cdot \sum J_{\text{B1}}[N] + J_{\text{TIN}}[N] + J_{\text{CK}}[N] \right)$$

$$+ F_{\text{B2}} \cdot \sum \Delta J_{\text{B2}} + F_{\text{A2}} \cdot \sum \Delta J_{\text{A2}} + A_2(\Delta J_{\text{HL}} + \Delta J_{\text{LH}} + T_{\text{CK}}) + F_{\text{A2}} \cdot \Delta^2 Q N_2,$$

(4)

Therein,  $A_1$  and  $A_2$  are constants. In this case,  $A_1$  equals  $F_{A1} - F_{B1}$ .  $A_2$  equals  $F_{A2} - F_{B2}$ . A frequency mismatch between the two FSOs can be canceled out using a first-order least mean squares (LMS) filter in the DSP [3].

Equation (4) shows that the timing jitters and the oscillator jitters at the first stage ( $\Sigma J_{A1}$ ,  $\Sigma J_{B1}$ ,  $J_{TIN}$  and  $J_{CK}$ ) are not noise-shaped. They remain as noise sources. Therefore, they affect the resolution of the first- and second-order FSOTDCs directly. These jitters must be reduced for high resolution. Actually,  $\Delta J_{LH}$  and  $\Delta J_{HL}$  are noise-shaped, so they are cancelled out as noise sources.

# 2.1 Effect of FSO Jitters ( $\Sigma J_{A1}$ , $\Sigma J_{B1}$ )

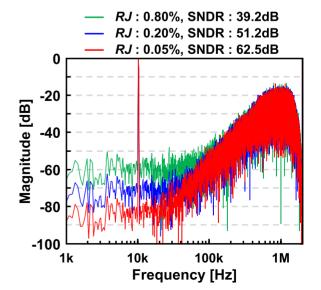

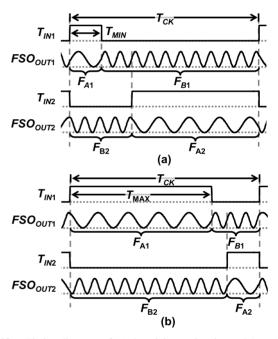

In this subsection, we present discussion of the effects of the FSO jitters:  $J_{A1\_X}$ ,  $J_{B1\_X}$ ,  $J_{A2\_X}$ , and  $J_{B2\_X}$ . The jitters of the second-stage FSO  $(J_{A2}X)$  and  $J_{B2}X$  are first-order noise-shaped, as described above. Therefore, we exclude the effects of  $J_{A2}$  and  $J_{B2}$ . Then we define a relative jitter (RJ), which is a ratio of the jitter amount ( $J_{A1}$  and  $J_{\rm B1\_X}$ ) to the oscillation period of the first-stage FSO (1/ $F_{\rm A1}$ and  $1/F_{\rm B1}$ ), and which is an important parameter affecting the TDC resolution. Actually, RJ is defined as the ratio of the oscillator cycle jitter's standard deviation to the cycle period. Figure 2 shows the TDC output spectra and the SNDR at a bandwidth of 20 kHz, obtained with MATLAB, for RJ amounts of 0.05%, 0.2%, and 0.8%. This paper utilizes the same MATLAB simulation which has been proposed in [3]. The simulation requires the FSO frequency and the RJ; we achieve these parameters from SPICE simulation. Because the jitters of the first-stage FSO are not first-order noise-shaped, the noise floor increases depending on RJ and decreases the SNDR. RJ is expected to be about 0.05% to achieve 10-bit resolution. In [4], the standard deviation of a ring oscillator's jitter ( $\sigma$ ) model is

$$\sigma^2 = \frac{kT}{IF_0} \cdot \left( \frac{2}{V_{\rm DD} - V_{\rm TH}} \left( \gamma_{\rm N} + \gamma_{\rm P} \right) + \frac{2}{V_{\rm DD}} \right),\tag{5}$$

where  $F_0$  stands for the output frequency of the ring oscillator. k denotes the Boltzmann's constant.  $V_{\rm TH}$  is a threshold voltage. In addition, T,  $V_{\rm DD}$ , and I respectively represent the temperature, a supply voltage and a current for the oscillator.  $\gamma_{\rm N}$  and  $\gamma_{\rm P}$  are parameters of NMOS and PMOS. Therefore, RJ can be given as

$$RJ = F_0 * \sigma = \sqrt{\frac{kTF_0}{I} \cdot \left(\frac{2}{V_{\text{DD}} - V_{\text{TH}}} (\gamma_{\text{N}} + \gamma_{\text{P}}) + \frac{2}{V_{\text{DD}}}\right)}.$$

(6)

Fig. 2 Output spectra when RJ is varied.

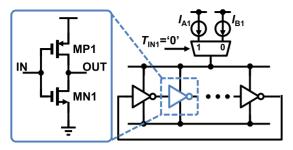

Fig. 3 Simulation model of an FSO.

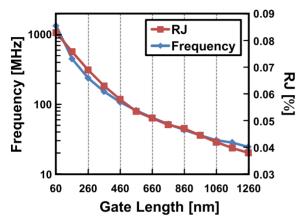

**Fig. 4** Relative jitter (RJ) and oscillation frequency with sweeping gate length from 60 nm to 1260 nm.

From [4],  $F_0$  is given as

$$F_0 \cong \frac{I}{MCV_{DD}}. (7)$$

where C is a load capacitance of the inverter, and M is the number of oscillator stages. (6) is rewritten as

$$RJ \cong \sqrt{\frac{kT}{MCV_{DD}}} \cdot \left(\frac{2}{V_{DD} - V_{TH}} (\gamma_{N} + \gamma_{P}) + \frac{2}{V_{DD}}\right).$$

(8)

From (8), RJ is affected by C, M,  $V_{\rm DD}$  and T. We conducted transient noise analyses in SPICE to examine the relation among RJ, the oscillation frequency, and the current amount with variation of the gate length of the oscillator. Figure 3 presents a simulation model of the FSO. In these simulations, the sampling rate (SR) is 2 MHz, the band-width (BW) is 20 kHz and the full-range input time interval is 250 ns.

# 2.1.1 Gate Length

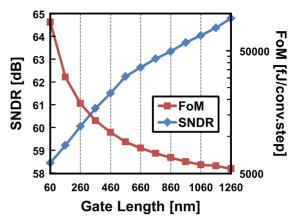

In this simulation, the gate length of the inverters (MP1 and MN1) in the 17-stage ring oscillator is swept from 60 nm to 1260 nm. The simulation time is 200 times longer than the longest oscillator period. As presented in Fig. 4, *RJ* tends to be small for a low oscillation frequency. *RJ* with the largegate length results in approximately 0.04%. Figure 5 shows that the lower *RJ* improves the SNDR. These simulations demonstrate that *RJ* is reduced under 0.055% and that 10-bit resolution is achievable at the slow oscillation frequency

Fig. 5 SNDR and FoM with sweeping gate length from 60 nm to 1260 nm.

**Fig. 6** SNDR and FoM with sweeping M from 3 to 17.

for 560 nm gate length. A figure-of-merit (FoM) is also depicted in Fig. 5. The FoM is improved by the large-gate inverter because the large capacitance.

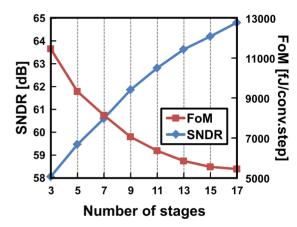

# 2.1.2 Number of Oscillator Stages

$F_0$  is inversely proportional to M from (7). RJ is inversely proportional to the square root of M from (8). In this simulation, M is swept from 3 to 17. The gate length is 1260 nm,  $V_{\rm DD}$  is 1.5 V, and T is 25°C. With more-stage FSO, RJ becomes lower. The SNDR becomes higher and the FoM are improved with more-stage FSO as presented in Fig. 6.

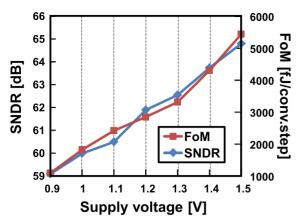

### 2.1.3 Supply Voltage

RJ is also inversely proportional to the square root of  $V_{\rm DD}$ . In this simulation,  $V_{DD}$  in the ring oscillator is swept from 0.9 V to 1.5 V. The gate length is 1260 nm, M is 17, and T is 25°C. As higher  $V_{\rm DD}$ , the oscillator achieves the higher frequency and the lower RJ. The SNDR becomes higher as  $V_{\rm DD}$  becomes larger in Fig. 7. However the power consumption is increased at the higher  $V_{\rm DD}$  and the FoM is worsen. There is a trade-off relationship between SNDR and FoM, when  $V_{\rm DD}$  is swept.

Fig. 7 SNDR and FoM with sweeping  $V_{DD}$  from 0.9 V to 1.5 V.

**Fig. 8** SNDR and FoM with sweeping T from  $0^{\circ}$ C to  $100^{\circ}$ C.

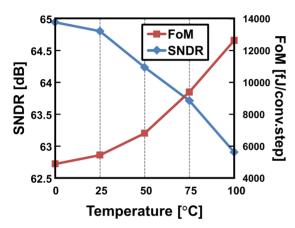

# 2.1.4 Temperature

In this section, we discuss the effect of the temperature. RJ is inversely proportional to the square root of T. We sweep T from 0°C to 100°C. The gate length is 1260 nm,  $V_{\rm DD}$  is 1.5 V, and M is 17. As presented in Fig. 8, at the lower temperature, the SNDR and the FoM is improved because the FSO achieves lower RJ and higher  $F_0$ .

# 2.2 Relation between FSO Frequency and Sampling Rate $(F_{A1}, F_{B1}, F_{A2}, F_{B2}, \text{ and } T_{CK})$

When the FSO frequency becomes lower, its sampling rate in the FSOTDC must be decreased. This subsection presents discussion of the relation between the FSO frequency and its sampling rate. The FSOTDC needs at least one respective rising edge during  $T_{\rm INI}$  and  $T_{\rm CK}-T_{\rm INI}$ .

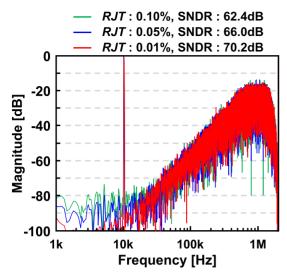

$QN_1$  is propagated to the next stage by the QNP. Figures 9(a) and 9(b) respectively present a schematic and an example of the timing diagram in the QNP. The QNP consists of two dynamic d-type flipflops (DDFFs) and an NOR gate to avoid metastability [5]. To propagate  $QN_1$ , the QNP requires two rising edges or more in each sampling cycle. Figure 10 portrays a timing diagram with the minimum and

**Fig. 9** (a) Schematic and (b) timing diagram of the quantization noise propagator (QNP).

**Fig. 10** Timing diagrams of (a) the minimum time interval  $(T_{\rm MIN})$  and (b) the maximum time interval  $(T_{\rm MAX})$ .

the maximum  $T_{\rm IN1}$  ( $T_{\rm MIN}$  and  $T_{\rm MAX}$ :  $T_{\rm MAX}-T_{\rm MIN}$  is a dynamic range).  $T_{\rm MIN}$  must be longer than  $1/F_{\rm A1}$ . There should exist two rising edges in  $T_{\rm CK}-T_{\rm MAX}$  and one rising edge in  $T_{\rm IN2}$  at least. Therefore, the relation of FSO frequency and  $T_{\rm MAX}$  is  $T_{\rm CK}-T_{\rm MAX}>1/F_{\rm B1}+1/F_{\rm A2}$ . Eventually, in the two-stage FSOTDC, the range of  $T_{\rm IN1}$  is

$$\frac{1}{F_{\rm A1}} < T_{\rm IN1} < T_{\rm CK} - \left(\frac{1}{F_{\rm B1}} + \frac{1}{F_{\rm A2}}\right). \tag{9}$$

# 2.3 Effect of Input and Clock Jitters ( $J_{TIN}$ and $J_{CK}$ )

Next, we discuss the clock jitter effect. Here, clock jitter includes  $T_{\rm IN1}$  and  $T_{\rm IN2}$  jitters. We define the ratio of the clock jitter's standard deviation to the  $T_{\rm CK}$  as RJT. The  $T_{\rm IN2}$  jitters ( $J_{\rm LH}$  and  $J_{\rm HL}$ ) achieve first-order noise shaping. Therefore, we define that the RTJ equals  $J_{\rm TIN}/T_{\rm CK}$  and  $J_{\rm CK}/T_{\rm CK}$ . Figure 11 shows the SNDRs for RJT of 0.10%, 0.05%, and

Fig. 11 Output spectra when CK jitter is varied.

0.01%. In this MATLAB simulation, RJ is 0% and  $T_{\rm CK}$  is  $500\,\rm ns$ . The noise floor increases depending on the clock jitter. Therefore, it decreases the SNDR. RJT should be reduced to 0.10% or less for 10-bit resolution.

# 3. Measurement Results of Low-Jitter FSOTDC Test Chip and Comparison to the Analyses

Based on the discussion presented in Sect. 2, we developed a low-noise FSO architecture to increase the resolution. To realize the small-area 10-bit TDC, we improve a low-noise 17-stage FSO with large-gate inverters. In SPICE simulation, the RJ of the ring oscillator is 0.038% considering current sources,  $F_{\rm A1.2}$  is 17 MHz, and  $F_{\rm B1.2}$  is 25 MHz.

To obtain a second-order noise shaping characteristic, the FSOTDC requires detection of the quantization noise. The FSO must oscillate sufficiently during the  $T_{\rm IN1}$  pulse width for the QNP to operate correctly, as described in Sect. 2.2. Here, the sampling clock is 2 MHz. The full-range of the  $T_{\rm IN1}$  is 250 ns. Figure 12 presents a MATLAB simulation result of the FSOTDC. The SNDR of 64.8 dB is achievable at a 20-kHz bandwidth. In this result, this FSOTDC achieves 10-bit resolution.

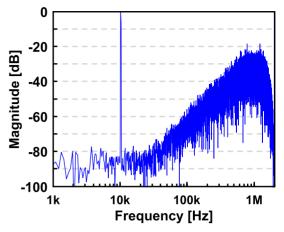

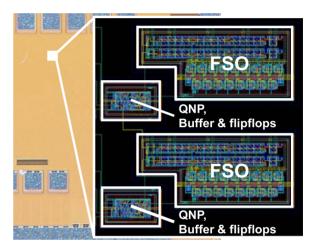

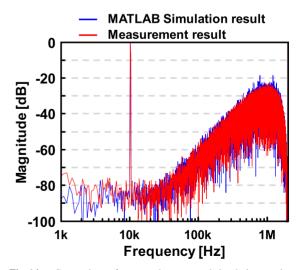

A test chip was fabricated using a 65-nm CMOS process (Fig. 13). The 1.5-V TDC core occupies  $597 \, \mu \text{m}^2$  as an active area. Figure 14 shows the spectra obtained from the simulated and measured output of the proposed TDC with the LMS filter. In the spectra, the input signal frequency is  $10 \, \text{kHz}$ ; the input width is  $250 \, \text{ns}$  at a  $2 \, \text{MHz}$  sampling rate. The SFDR is  $75.4 \, \text{dB}$ . The SNDR is  $64.5 \, \text{dB}$ , which is worse than that in the simulation because of the effect of the 1/f noise at low frequency. The test chip performance is presented in Table 1. The FSOs consume  $218 \, \mu \text{W}$ . The QNP, peripheral buffers, and flip-flops consume  $113 \, \mu \text{W}$ . In comparison with [3], this test chip has higher resolution because RJ is lower. However, the sampling rate is lower and the power consumption is increased. Therefore, the figure-

Fig. 12 Simulation result of low jitter second-order FSOTDC.

Fig. 13 Chip micrograph and layout of the 65 nm proposed FSOTDC.

Fig. 14 Comparison of measured spectra and simulation results.

of-merit (FoM) is worsened.

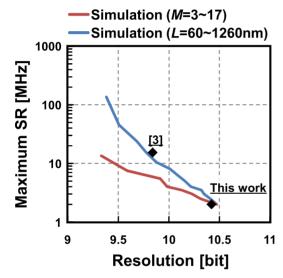

Figure 15 presents the performance of the FSOTDC using the simulation result in Sect. 2. In these simulations with

| Item                 | [3]    | This<br>work |

|----------------------|--------|--------------|

| Technology (nm)      | 65     | 65           |

| Bandwidth (kHz)      | 500    | 20           |

| Sampling rate (MS/s) | 16     | 2            |

| Power (mW)           | 0.282  | 0.332        |

| SNDR (dB)            | 61     | 64.5         |

| ENOB (bits)          | 9.8    | 10.4         |

| Active area (mm²)    | 0.0007 | 0.0006       |

| FoM(fJ/conv.step)    | 308    | 6050         |

Fig. 15 Simulation and measurement results of FSO TDC performance.

sweeping gate length and M, the input width is a half of SR, SR is maximum frequency which is calculated with (9), and an oversampling rate (OSR) is 50. To achieve higher resolution the FSOTDC at the same sampling rate, one can increase the channel length and transistor width to decrease RJ.

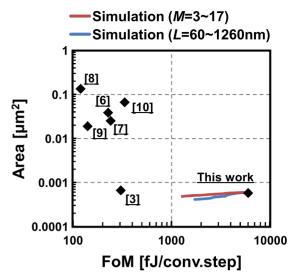

FSOTDCs with large-gate and many-stages achieve the high ENOB. However the active area becomes larger. Figure 16 shows the relationship of the active area and the FoM at the maximum *SR*. And we compare the other state-of-the-art TDCs. The state-of-the-art TDCs have lower FoM, but they occupy large active area. The estimated area of the FSOTDC is calculated by using the active area. Based on these simulation results, the FoM of the FSOTDCs with the smaller-gate and fewer-stage FSOs tends to decrease. Because the FSO frequencies become higher, the maximum *SR* and the maximum *BW* are also higher. On the other hand, the ENOB at the maximum *BW* is increased by the largegate inverters and many-stages FSOs. Therefore, there is a trade-off between ENOB and FoM.

Fig. 16 Simulation results and comparison with other state-of-the-art TDCs.

#### 4. Conclusion

By analyzing the second-order FSOTDC, we demonstrated that the noise floor of the TDC is determined by the oscillator timing jitters and that they occupy the TDC resolution. To implement lower-jitter FSO, we introduced largegate inverter rings. In a standard 65-nm CMOS process, we designed a 10-bit FSOTDC using our design methodology. Results show that our design methodology is available for estimating FSOTDC performance by comparison to a test chip.

#### Acknowledgments

This development was performed by the author for STARC as part of the Japanese Ministry of Economy, Trade and Industry sponsored "Silicon Implementation Support Program for Next Generation Semiconductor Circuit Architectures." The chip design was supported by the VLSI Design and Education Center (VDEC) of the University of Tokyo in collaboration with Synopsys Inc., Cadence Design Systems Inc., and Mentor Graphics Corp.

#### References

- S. Song, B. Kim, and V. Stojanović, "A fractionally spaced linear receive equalizer with voltage-to-time conversion," IEEE Symp. on VLSI Circuits, pp.222–223, 2009.

- [2] J.S. Tandon, T.J. Yamaguchi, S. Komatsu, and K. Asada, "A stochastic sampling time-to-digital converter with tunable 180–770 fs resolution, INL less than 0.6LSB, and selectable dynamic range offset," Proc. IEEE 2013 Custom Integrated Circuits Conf., pp.1–4, Sept. 2013.

- [3] T. Konishi, K. Okuno, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "A second-order all-digital TDC with low-jitter frequency shift oscillators and dynamic flipflops," IEICE Trans. Electron., vol.E96-C, no.4, pp.546–552, April 2013.

- [4] A.A. Abidi, "Phase noise and jitter in CMOS ring oscillators," IEEE

- J. Solid-State Circuits, vol.41, no.8, pp.1803-1816, Aug. 2006.

- [5] K. Okuno, T. Konishi, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "A 62-dB SNDR second-order gated ring oscillator TDC with two-stage dynamic D-type flipflops as a quantization noise propagator," IEEE International New Circuits and Systems (NEWCAS), pp.289–292, 2012.

- [6] M.Z. Straayer and M.H. Perrott, "A multi-path gated ring oscillator TDC with first-order noise shaping," IEEE J. Solid-State Circuits, vol.44, no.4, pp.1089–1098, May, 2009.

- [7] S. Mandai and E. Charbon, "A 128-channel, 9 ps column-parallel two-stage TDC based on time difference amplification for time-resolved imaging," Proc. IEEE ESSCIRC, pp.119–122, Sept. 2011.

- [8] K.S. Kim, W.S. Yu, and S.H. Cho, "A 9b, 1.12 ps resolution 2.5 b/Stage pipelined time-to-digital converter in 65 nm CMOS using time-register," IEEE Symp. on VLSI Circuits, pp.136–137, 2013

- [9] K.S. Kim, Y.H. Kim, W.S. Yu, and S.H. Cho, "A 7b, 3.75 ps resolution two-step time-to-digital converter in 65 nm CMOS using pulse–train time amplifier," IEEE Symp. on VLSI Circuits, pp.192–193, June 2012.

- [10] Y.-H. Seo, J.-S. Kim, H.-J. Park, and J.-Y. Sim, "A 1.25 ps resolution 8b cyclic TDC in 0.13  $\mu$ m CMOS," IEEE J. Solid-State Circuits, vol.47, no.3, pp.736–743, March 2012.

Masahiko Yoshimoto joined the LSI Laboratory, Mitsubishi Electric Corporation, Itami, Japan, in 1977. From 1978 to 1983, he had been engaged in the design of NMOS and CMOS static RAM. Since 1984 he had been involved in the research and development of multimedia ULSI systems. He earned a Ph.D. degree in Electrical Engineering from Nagoya University, Nagoya, Japan in 1998. Since 2000, he had been a professor of Dept. of Electrical & Electronic System Engineering in Kanazawa Univer-

sity, Japan. Since 2004, he has been a professor of Dept. of Computer and Systems Engineering in Kobe University, Japan. His current activity emphasizes the research and development of an ultra-low power multimedia and ubiquitous media VLSI systems and a dependable SRAM circuit. He holds 70 registered patents. He has served on the program committee of the IEEE International Solid State Circuit Conference from 1991 to 1993. Additionally, he served as Guest Editor for special issues on Low-Power System LSI, IP and Related Technologies of IEICE Transactions in 2004. He was a chair of IEEE Solid State Circuits Society (SSCS) Kansai Chapter from 2009 to 2010. He is also a chair of the IEICE Electronics Society Technical Committee on Integrated Circuits and Devices from 2011–2012. He received the R&D100 awards from the R&D magazine for the development of the DISP and the development of the real-time MPEG2 video encoder chipset, respectively, in 1990 and 1996. He also received the 21st TELECOM System Technology Award in 2006.

Keisuke Okuno received a B.E. and M.Eng. degree in Computer and Systems Engineering from Kobe University, Hyogo, Japan in 2011 and 2013. Currently, he is a Ph.D. candidate at Kobe University. His current research interests include digital signal processing and adaptive filters. He is a member of the IEEE.

**Toshihiro Konishi** received B.Eng. and M.Eng. degrees in Computer Science and Systems Engineering from Kobe University, Hyogo, Japan in 2008 and 2010, respectively, where he is currently a Ph.D. candidate. He researches low-power digitally controlled oscillators, analog-to-digital converters, time-to-digital converter designs, digitally assisted analog signal processing, and digital signal processing. He is a member of the IEEE and IEICE.

Shintaro Izumi respectively received B.Eng. and M.Eng. degrees in Computer Science and Systems Engineering from Kobe University, Hyogo, Japan, in 2007 and 2008. He received his Ph.D. degree in Engineering from Kobe University in 2011. He was a JSPS Research Fellow at Kobe University from 2009 to 2011. Since 2011, he has been an Assistant Professor in the Organization of Advanced Science and Technology at Kobe University. His current research interests include biomedical signal

processing, communication protocols, low-power VLSI design, and sensor networks. He is a member of the IEEE, IEICE, and IPSJ.

Hiroshi Kawaguchi received B.Eng. and M.Eng. degrees in electronic engineering from Chiba University, Chiba, Japan, in 1991 and 1993, respectively, and earned a Ph.D. degree in electronic engineering from The University of Tokyo, Tokyo, Japan, in 2006. He joined Konami Corporation, Kobe, Japan, in 1993, where he developed arcade entertainment systems. He moved to The Institute of Industrial Science, The University of Tokyo, as a Technical Associate in 1996, and was appointed as a Research

Associate in 2003. In 2005, he moved to Kobe University, Kobe, Japan. Since 2007, he has been an Associate Professor with The Department of Information Science at that university. He is also a Collaborative Researcher with The Institute of Industrial Science, The University of Tokyo. His current research interests include low-voltage SRAM, RF circuits, and ubiquitous sensor networks. Dr. Kawaguchi was a recipient of the IEEE ISSCC 2004 Takuo Sugano Outstanding Paper Award and the IEEE Kansai Section 2006 Gold Award. He has served as a Design and Implementation of Signal Processing Systems (DISPS) Technical Committee Member for IEEE Signal Processing Society, as a Program Committee Member for IEEE Custom Integrated Circuits Conference (CICC) and IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips), and as an Associate Editor of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and IPSJ Transactions on System LSI Design Methodology (TSLDM). He is a member of the IEEE, ACM, IEICE, and IPSJ.