# on Fundamentals of Electronics, Communications and Computer Sciences

VOL. E97-A NO. 12 DECEMBER 2014

The usage of this PDF file must comply with the IEICE Provisions on Copyright.

The author(s) can distribute this PDF file for research and educational (nonprofit) purposes only.

Distribution by anyone other than the author(s) is prohibited.

PAPER Special Section on VLSI Design and CAD Algorithms

# STT-MRAM Operating at 0.38 V Using Negative-Resistance Sense Amplifier

Yohei UMEKI<sup>†a)</sup>, Student Member, Koji YANAGIDA<sup>†</sup>, Nonmember, Shusuke YOSHIMOTO<sup>††</sup>, Shintaro IZUMI<sup>†</sup>, Masahiko YOSHIMOTO<sup>†</sup>, Hiroshi KAWAGUCHI<sup>†</sup>, Members, Koji TSUNODA<sup>†††</sup>, and Toshihiro SUGII<sup>†††</sup>, Nonmembers

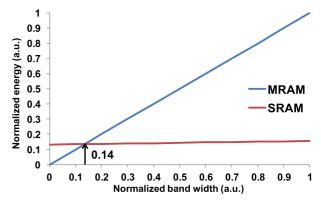

SUMMARY This paper reports a 65 nm 8 Mb spin transfer torque magnetoresistance random access memory (STT-MRAM) operating at a single supply voltage with a process-variation-tolerant sense amplifier. The proposed sense amplifier comprises a boosted-gate nMOS and negative-resistance pMOSs as loads, which maximizes the readout margin at any process corner. The STT-MRAM achieves a cycle time of  $1.9\,\mu\mathrm{s}$  (=  $0.526\,\mathrm{MHz}$ ) at  $0.38\,\mathrm{V}$ . The operating power is  $1.70\,\mu\mathrm{W}$  at this voltage. The minimum energy per access is  $1.12\,\mathrm{pJ/bit}$  when the supply voltage is  $0.44\,\mathrm{V}$ . The proposed STT-MRAM operates at a lower energy than an SRAM when the utilization of the memory bandwidth is 14% or less.

key words: STT-MRAM, low-voltage, process-variation-tolerant

#### 1. Introduction

The capacity of embedded memory on a chip has been increasing. In fact, the ITRS predicts that the leakage power in embedded memory will account for 40% of all power consumption by 2024 [1]. A spin transfer torque magnetoresistance random access memory (STT-MRAM), which stores data as magnetic resistance states, is promising for use as non-volatile memory to reduce the leakage power. It is useful as embedded memory because it can function at low voltages and has a lifetime of over 10<sup>16</sup> write cycles [2]. In addition, STT-MRAM technology has a smaller bitcell than an SRAM, making STT-MRAM suitable for use in high-density products [3]–[7].

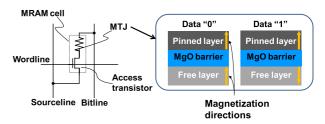

Figure 1 shows a schematic 1T1MTJ bitcell with one transistor and one magnetic tunnel junction (MTJ) STT-MRAM bitcell. The MTJ is a magnetoresistive device and has pinned and free layers with a tunnel barrier (MgO barrier) between them as an insulator. The MTJ has two states: a parallel state and an antiparallel state. The magnetization direction of the free layer determines the state. In the free layer, the magnetization direction can be switched by the current flowing through the MTJ, which corresponds to a datum stored in a bitcell. The MTJ resistances are low and high in the parallel and antiparallel states, respectively. In

Manuscript received March 19, 2014.

Manuscript revised June 30, 2014.

<sup>†</sup>The authors are with the Graduate School of System Informatics, Kobe University, Kobe-shi, 657-8501 Japan.

††The author is with the Department of Electrical Engineering, Stanford University, Gates 337, 353 Serra Mall, Stanford, CA, 94305, USA.

†††The authors are with the Low-Power Electronics Association and Project (LEAP), Tsukuba-shi, 305-8569 Japan.

a) E-mail: umeki@cs28.cs.kobe-u.ac.jp DOI: 10.1587/transfun.E97.A.2411

Fig. 1 STT-MRAM bitcell.

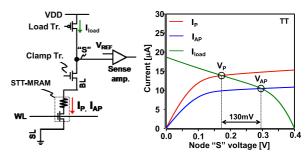

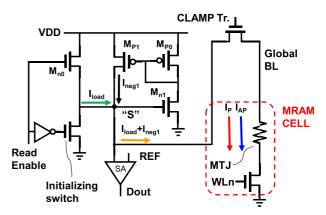

Fig. 2 Conventional read circuit and bias condition at TT corner.

the read operation, the stored datum is read out as the difference in the flowing current.

Although the MTJ has the potential to operate at less than 0.4 V [8], such low-voltage operation has not been demonstrated to date for an STT-MRAM macro because the design of the peripheral circuitry is difficult. A pMOS load sense amplifier [8] or a sense amplifier with an op-amp for a replica bias [9] does not function at such a low voltage.

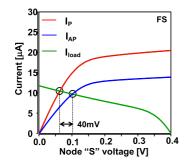

Figure 2 shows a conventional read circuit [8] and its bias condition at a supply voltage of 0.4 V. This readout circuit draws a read current I<sub>load</sub> to the STT-MRAM cell. The voltage of node "S" is determined by the cell datum because the resistance of the STT-MRAM is dependent on the state of the MTJ. Specifically, the voltage at node "S" is determined by the balance of I<sub>load</sub> and the cell current (I<sub>P</sub> or I<sub>AP</sub>) as shown in the figure. The sense amplifier can distinguish the datum, for instance, at a typical process corner where the voltage difference between the parallel and antiparallel states is sufficiently larger than the offset voltage of the sense amplifier. Figure 3 shows another bias condition at the FS corner; the conventional read circuit, however, cannot operate at 0.4 V because the voltage difference at node "S" becomes as small as 40 mV, which is insufficient to operate the sense amplifier.

Fig. 3 Bias condition at FS corner in the conventional read circuit.

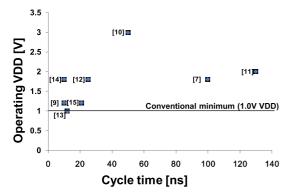

Fig. 4 Conventional operating VDDs and cycle times.

Figure 4 shows operating VDDs and cycle times of conventional STT-MRAM in previous studies [7], [9]–[15]. The operating voltage in these studies was 1.0 V or more, which indicates that it is difficult to realize peripheral circuits that can operate at low voltages. Herein, we present an STT-MRAM operating at a single 0.4 V supply voltage. Our proposed sense amplifier functions effectively below 0.4 V at any process corner, as a result of assistance from a charge pump circuit.

# 2. 8-Mb STT-MRAM Design

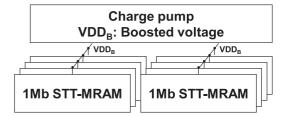

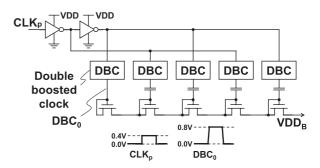

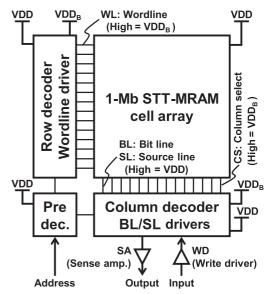

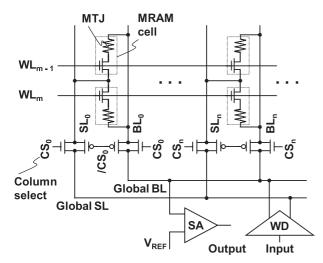

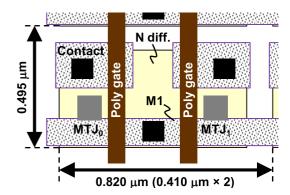

Figure 5 shows a macro-block diagram of the proposed 8 Mb STT-MRAM. A Dickson charge pump circuit provides a boosted voltage to eight 1 Mb STT-MRAM macros. A schematic of the charge pump circuit is depicted in Fig. 6. A 0.4 V clock swing is doubled to a 0.8 V amplitude by a double boosted clock (DBC) generator, which is then forwarded to a charge pump capacitor. The potential output voltage of this Dickson charge pump is  $3.0 \text{ V} = 5 (2 \text{ VDD} - V_{\text{thn}}) = 5$ (0.8 - 0.2)) because the clocking amplitude from the DBC generator is doubled to 0.8 V. In the macro, the supply voltage from the charge pump (VDD<sub>B</sub>) is controlled to 1.6 V so as not to damage the transistors. Figure 7 shows the block diagram of the macro and voltage domains of the 1 Mb STT-MRAM. The macro comprises four 256 kb blocks, each of which consists of 512 bits  $\times$  512 words. The supply voltage (VDD) is 0.4 V. Figure 8 shows the bitcell array and the peripheral circuits. To minimize the voltage drop through a bit line, a column selector using a transmission gate is adopted;

Fig. 5 Macro-block diagram of 8 Mb STT-MRAM.

**Fig. 6** Charge pump circuit and its waveforms.

Fig. 7 1-Mb STT-MRAM macro.

the gate voltage of the transmission gate is controlled with a boosted voltage (VDD<sub>B</sub>) of 1.6 V. In actual macro designs, the transmission gates connected to the global bit line and the global source line are located on opposite sides so that the sum of the wiring lengths of the bit line and the source line is the same for any STT-MRAM bitcell to balance the current path and voltage drop. Therefore, the parasitic resistance is the same in an STT-MRAM bitcell regardless of its position.

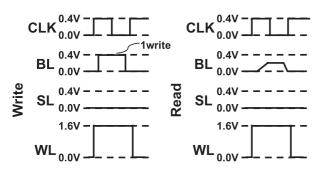

Figure 9 presents the operating waveforms. When writing the datum "1", the bit line (BL) is increased to  $0.4 \, \text{V}$ , whereas the source line (SL) is raised to  $0.4 \, \text{V}$  when writing the datum "0". VDD<sub>B</sub> is provided as a word line voltage,

Fig. 8 Bitcell array and peripheral circuits.

Fig. 9 Operating waveforms.

Fig. 10 SEM micrographs.

which suppresses the variation of the cell current caused by variations in the access transistors.

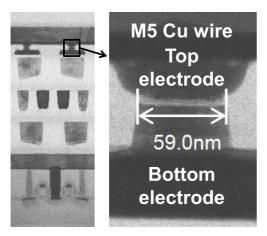

Figures 10 and 11 show SEM micrographs of a CoFeB-based MTJ and the STT-MRAM bitcell layout respectively. The dimensions of the MTJ are  $59 \times 59 \,\mathrm{nm^2}$ . The STT-MRAM process is the same as that described in earlier reports [2], [16].

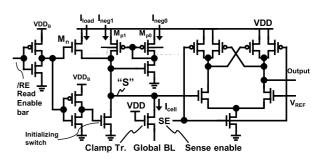

A detailed schematic of the proposed sense amplifier is shown in Fig. 12. The bitcell datum is determined by

Fig. 11 STT-MRAM bitcell layout.

Fig. 12 Proposed sens amplifier.

Fig. 13 Details of the current flowing through the proposed sense amplifier.

the voltage of node "S" and is input to the sense amplifier. Figure 13 shows details of the current flowing through the proposed circuit. In the initial state, the initializing switch grounds node "S". This cuts off the leakage current through  $M_{p0}$  ( $I_{neg0}$ ) in the current mirror of the negative-resistance pMOS load. In the read state, the "Read enable" signal becomes high and the nMOS load transistor ( $M_{n0}$ ) turns on. Then a load current ( $I_{load}$ ) flows from VDD. The voltage of node "S" is higher in the early phase of the read operation. This is because the output current from node "S" which flows to the clamp transistor and MRAM cell is smaller than the input current of node "S"  $I_{load}$ . When the voltage of node "S" becomes higher than  $V_{th}$  for  $M_{n1}$ ,  $M_{p1}$  drives the current

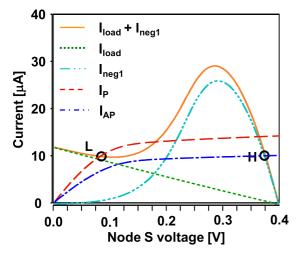

**Fig. 14** Current characteristics of sense amplifier at a typical (TT) proess corner.

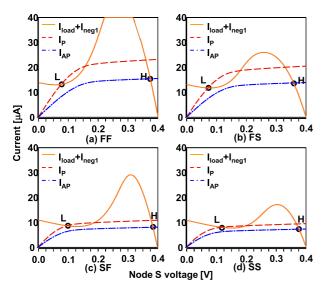

**Fig. 15** Current characteristics of sense amplifier at process corners: (a) FF, (b) FS, (c) SF, and (d) SS.

from VDD. The readout currents  $I_{load}$  and  $I_{neg1}$  flow from VDD, which exhibits 0.4 V operation. The boosted voltage of VDD<sub>B</sub> is used for the gate of the nMOS load transistor  $(M_n)$  and the initializing switch in the reading structure.

Figure 14 shows operating curves of the load circuits at a typical process corner (TT: pMOS = typical, nMOS = typical). The resistances of the MTJ are  $3.5\,\mathrm{k}\Omega$  and  $7\,\mathrm{k}\Omega$  respectively, in the parallel and antiparallel states. The total load current  $I_{cell} = I_{load} + I_{neg1}$  is a function of the voltage of node "S". The intersection of the load current and  $I_P$  ("L") or  $I_{AP}$  ("H") results in  $I_{cell}$ . The voltage difference between "L" and "H" is greater than 250 mV, which is much more than that of a conventional pMOS load circuit [3]; VDD/2 is effective as a reference voltage ( $V_{REF}$ ). The size of the boosted nMOS load Mn can be reduced (moreover, its standby leakage can be reduced) because it operates in a linear region by virtue of its boosted voltage. Therefore, the load cur-

Fig. 16 Waveforms obtained by Monte Carlo simulation.

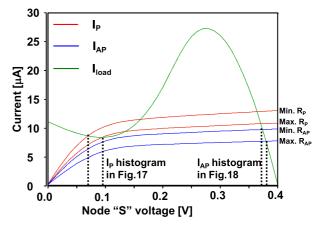

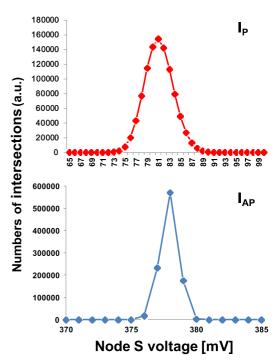

**Fig. 17** Histograms of the node "S" voltage at the intersections of  $I_{load}$  with  $I_P$  and  $I_{AP}$ .

rent is sufficient even with a small transistor. The proposed sense amplifier is tolerant to process variations, as shown in Figs. 15(a)–15(d). Even at the FF, FS, SF, and SS corners, the proposed sense amplifier can distinguish parallel from antiparallel states.

Figure 16 shows the results of a Monte Carlo simulation of the proposed circuit. The number of trials is 1 M. The simulation was performed by varying the MTJ and the access transistor at the TT corner. In the figure, the minimum and maximum values of  $I_P$  and  $I_{AP}$  are shown. Figure 17 shows histograms of the voltage of node "S" in the  $10^6$  Monte Carlo simulations at the intersections of  $I_{load}$  with  $I_P$  and  $I_{AP}$ . The proposed circuit is tolerant to variations in both the MTJ and the access transistor.

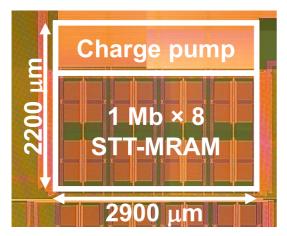

Fig. 18 Chip photograph

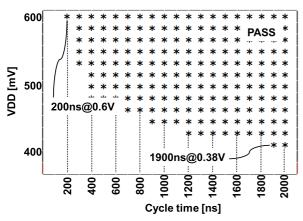

Fig. 19 Shmoo plot.

## 3. Chip Implementation and Measurement Results

We fabricated a 65 nm test chip at the TT process corner, as shown in Fig. 18, to evaluate the low-voltage and low-leakage operation. The detailed fabrication process of the MTJ device used in the test chip is presented in references [2], [16]. The macro size is  $2.2 \times 2.9 \,\mathrm{mm^2}$ . Figure 19 shows a Shmoo plot of the test chip. We confirmed operation at 0.38 V for a cycle time of  $1.9\,\mu\mathrm{s}$  (the operating frequency is therefore  $0.526\,\mathrm{MHz}$ ); under these conditions the operating power is  $1.70\,\mu\mathrm{W}$ . At this low voltage, the read operation is achieved using the proposed sense amplifier; the write operation is carried out by applying a long write pulse with a small write current.

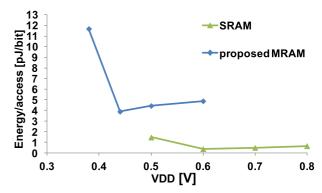

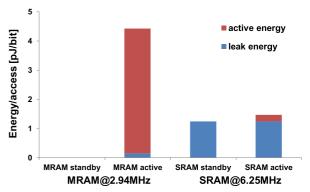

Figure 20 shows the energy consumption of the proposed STT-MRAM and a low-voltage SRAM [17] fabricated with the same process technology. Both sets of results are measured values. The ratio of read to write accesses is 50:50. At an operating voltage of 0.5 V, the energy consumed by the STT-MRAM is 3.03 times larger than that consumed by the SRAM. Figure 21 presents a breakdown of the energy components. The ratios of active energy ( $E_{active}$ ) to total energy ( $E_{active}$ ) are 96.7% and 15.4% in the

Fig. 20 Energy/bit comparison between the proposed STT-MRAM and a conventional SRAM.

$Fig.\,21$   $\,\,$  Energy breakdown in the STT-MRAM and SRAM at VDD of 0.5 V.

Fig. 22 Energy versus utilization of memory band width in the STT-MRAM and SRAM.

STT-MRAM and SRAM, respectively. Figure 22 shows an comparison of the energy when the utilization of the memory bandwidth is changed. The STT-MRAM is superior to the SRAM in terms of energy consumption if the utilization of the memory bandwidth is 14% or less, which means that the STT-MRAM is suitable for use in less active applications such as the healthcare systems and sensor networks. Table 1 shows the characteristics of the test chip.

|                     | *                    |

|---------------------|----------------------|

| Process technology  | 65nm bulk CMOS       |

| Nominal voltage     | 1.2V                 |

| Charge pump output  | 1.6V                 |

| Capacity            | 8Mb                  |

| Cell size           | 0.203μm²             |

|                     | (0.495µmx0.41µm)     |

| Operating VDD       | 0.38V-0.6V           |

| Oparating frequency | 0.536MHz-5.00MHz     |

| Oparating power     | 1.70µW@0.526MHz      |

| Minimum energy      | 1.12 pJ/bit          |

| per access          | at 0.44V and 1.66MHz |

| Charge pump output  | 1.6V                 |

Table 1 Test chip characteristics.

#### 4. Conclusion

We presented a new sense amplifier with tolerance to process valiations for an STT-MRAM operating at low voltages. The proposed sense amplifier can distinguish between parallel and antiparallel states at all process corners. We fabricated an 8 Mb STT-MRAM using a 65 nm process technology. The test chip exhibits 0.38 V operation at a frequency of 0.526 MHz, at which the power consumption is  $1.70\,\mu\text{W}$ . The proposed STT-MRAM operates at a lower energy than an SRAM when the utilization of the memory bandwidth is 14% or less.

### Acknowledgments

We would like to thank Toppan Technical Design Center Co., Ltd., for chip implementation. This work was performed as the "Ultra-Low Voltage Device Project" of the Low-power Electronics Association & Project (LEAP) funded and supported by METI and NEDO. Part of the device processing was performed by AIST, Japan.

#### References

- [1] International Technology Roadmap for Semiconductors (ITRS), http://www.itrs.net/

- [2] C. Yoshida, T. Ochiai, Y. Iba, Y. Yamazaki, K. Tsunoda, A. Takahashi, and T. Sugii, "Demonstration of non-volatile working memory through interface engineering in STT-MRAM," IEEE VL-SIT, pp.59–60, June 2012.

- [3] R. Leuschner, U.K. Klostermann, H. Park, F. Dahmani, C. Grigis, K. Harnan, S. Mege, C. Park, M.C. Clech, G.Y. Lee, S. Bournat, L. Altimime, and G. Mueller, "Thermal select MRAM with a 2-bit cell capability for beyond 65 nm technology node," IEEE IEDM, pp.165–168, Dec. 2006.

- [4] S. Tehrami, "Status and outlook of MRAM memory technology," IEEE IEDM, pp.585–588, Dec. 2006.

- [5] N. Sakimura, T. Sugibayashi, T. Honda, H. Honjo, S. Saito, T. Suzuki, N. Ishiwata, and S. Tahara, "MRAM cell technology for over 500 MHz SoC," IEEE VLSIC, pp.108–109, June 2006.

- [6] M. Hosomi, H. Yamagishi, T. Yamamoto, K. Bessho, Y. Higo, K. Yamane, H. Yamada, M. Shoji, H. Hachino, C. Fukumoto, H. Nagao, and H. Kano, "A novel nonvolatile memory with spin torque transfer magnetization switching: Spin-ram," IEEE IEDM, pp.459–462, Dec. 2005.

- [7] T. Kawahara, R. Takemura, K. Miura, J. Hayakawa, S. Ikeda, Y. Lee, R. Sasaki, Y. Goto, K. Ito, T. Meguro, F. Matsukura, H. Takahashi, H. Matsuoka, and H. Ono, "2 Mb spin-transfer

- torque RAM (SPRAM) with bit-by-bit bidirectional current write and parallelizing-direction current read," IEEE ISSCC, pp.480–481, Feb. 2007.

- [8] S. Matsunaga, S. Miura, H. Honjou, K. Kinoshita, S. Ikeda, T. Endoh, H. Ohno, and T. Hanyu, "A  $3.14\,\mu\text{m}^2$  4T-2MTJ-cell fully parallel TCAM based on nonvolatile logic-in-memory architecture," IEEE VLSIC, pp.44–45, June 2012.

- [9] D. Halupka, S. Huda, W. Song, A. Sheikholeslami, K. Tsunoda, C. Yoshida, and M. Aoki, "Negative-resistance read and write schemes for STT-MRAM in 0.13 μm CMOS," IEEE ISSCC, pp.256–257, Feb. 2010.

- [10] P.K. Naji, M. Durlam, S. Tehrani, J. Calder, and M.F. DeHerrera, "A 246 kb 3.0 V 1T1MTJ nonvolatile magnetoresistive RAM," IEEE ISSCC, pp.122–123, Feb. 2001.

- [11] G. Jeong, W. Cho, S. Ahn, H. Jeong, G. Koh, Y. Hwang, and K. Kim, "A 0.24 μm 2.0 V 1T1MTJ 16 kb NV magnetoresistance RAM with self reference sensing," IEEE ISSCC, pp.280–281, Feb. 2003.

- [13] R. Nebashi, N. Sakimura, H. Honjo, S. Saito, Y. Ito, S. Miura, Y. Kato, K. Mori, Y. Ozaki, Y. Kobayashi, N. Ohshima, K. Kinoshita, T. Suzuki, K. Nagahara, N. Ishiwata, K. Suemitsu, S. Fukami, H. Hada, T. Sugibayashi, and N. Kasai, "A 90 nm 12 ns 32 Mb 2T1MTJ MRAM," IEEE ISSCC, pp.462–463, Feb. 2009.

- [14] J.P. Kim, T. Kim, W. Hao, H.M. Rao, K. Lee, X. Zhu, X. Li, W. Hsu, S.H. Kang, N. Matt, and N. Yu, "A 45 nm 1 Mb embedded STT-MRAM with design techniques to minimize read-disturbance," IEEE VLSIC, pp.296–297, June 2011.

- [15] M. Jefremow, T. Kern, W. Allers, C. Peters, J. Otterstedt, O. Bahlous, K. Hofmann, R. Allinger, S. Kassenetter, and D. Schmitt-Landsiedel, "Time-differential sense amplifier for sub-80 mV bitline voltage embedded STT-MRAM in 40 nm CMOS," IEEE ISSCC, pp.216–217, Feb. 2013.

- [16] Y. Iba, C. Yoshida, A. Hatada, M. Nakabayashi, A. Takahashi, Y. Yamazaki, H. Noshiro, K. Tsunoda, T. Takenaga, M. Aoki, and T. Sugii, "Top-pinned perpendicular MTJ structure with a counter bias magnetic field layer for suppressing a stray-field in highly scalable STT-MRAM," IEEE VLSIT, pp.136–137, June 2013.

- [17] S. Yoshimoto, M. Terada, S. Okumura, T. Suzuki, S. Miyano, H. Kawaguchi, and M. Yoshimoto, "A 40-nm 0.5-V 20.1-μW/MHz 8T SRAM with low-energy disturb mitigation scheme," IEEE VLSIC, pp.72–73, June 2011.

Yohei Umeki was born on December 20, 1985. He received a B.E. degree in Computer and Systems Engineering from Kobe University, Hyogo, Japan, in 2012. He is currently on a master courses at Kobe University. His current research is on low-power SRAM and low-voltage MRAM designs.

**Koji Yanagida** received a B.E. degree in Computer and Systems Engineering from Kobe University, Hyogo, Japan, in 2011. Currently, he is a master courses student at Kobe University. His current research is on low-voltage MRAM designs and low-power FeRAM designs.

Shusuke Yoshimoto received B.E. and M.E. degrees in Computer and Systems Engineering from Kobe University, Hyogo, Japan, in 2009 and 2011, respectively. He received Ph.D. degree in Engineering from the Kobe University in 2013. He moved to the Department of Electrical Engineering, Stanford University, as a Postdoc in 2013. His current research interests include testing, verification, nanoelectronics, and soft error, low-power and robust memory design. He was a recipient of 2011 and 2012 IEEE

SSCS Japan Chapter Academic Research Awards, a 2013 IEEE SSCS Kansai Chapter IMFEDK Student Paper Award and a 2013 Intel/Analog Devices/Catalyst Foundation/Cirrus Logic CICC Student Scholarship Award. He is a member of IEICE, IPSJ and IEEE. He was a representative for student members in the VDEC Designer's Forum Ph.D. session in 2012 and 2013. He is working on a member of ICD student TPC in 2012–2013. He is currently a Research Fellow of Japan Society for the Promotion of Science.

Shintaro Izumi received his B.Eng. and M.Eng. degrees in Computer Science and Systems Engineering from Kobe University, Hyogo, Japan, in 2007 and 2008, respectively. He received his Ph.D. degree in Engineering from Kobe University in 2011. He was a JSPS Research Fellow at Kobe University from 2009 to 2011. Since 2011, he has been an Assistant Professor in the Organization of Advanced Science and Technology at Kobe University. His current research interests include biomedical signal pro-

cessing, communication protocols, low-power VLSI design and sensor networks. He is a member of the IEEE, IEICE and IPSJ.

Masahiko Yoshimoto joined the LSI Laboratory, Mitsubishi Electric Corporation, Itami, Japan, in 1977. From 1978 to 1983 he was engaged in the design of NMOS and CMOS static RAM. Since 1984 he has been involved in the research and development of multimedia ULSI systems. He received a Ph.D. degree in Electrical Engineering from Nagoya University, Nagoya, Japan, in 1998. In 2000, he become a professor at the Dept. of Electrical & Electronic System Engineering in Kanazawa Univer-

sity, Japan. Since 2004, he has been a professor at the Dept. of Computer and Systems Engineering in Kobe University, Japan. His current activity is focused on the research and development of ultra low-power multimedia and ubiquitous media VLSI systems and a dependable SRAM circuit. He holds 70 registered patents. He served on the program committee of the IEEE International Solid State Circuit Conference from 1991 to 1993. He also served as Guest Editor for special issues on Low-Power System LSI, IP and Related Technologies of IEICE Transactions in 2004. He was a chair of IEEE SSCS (Solid State Circuits Society) Kansai Chapter from 2009 to 2010. He was also a chair of the IEICE Electronics Society Technical Committee on Integrated Circuits and Devices from 2011–2012. He received R&D100 awards from an R&D magazine for the development of the DISP and the real-time MPEG2 video encoder chipset in 1990 and 1996, respectively. He also received the 21st TELECOM System Technology Award in 2006.

Hiroshi Kawaguchi received B.Eng. and M.Eng. degrees in Electronic Engineering from Chiba University, Chiba, Japan, in 1991 and 1993, respectively, and received a Ph.D. degree in Electronic Engineering from the University of Tokyo, Tokyo, Japan, in 2006. He joined Konami Corporation, Kobe, Japan, in 1993, where he developed arcade entertainment systems. He moved to the Institute of Industrial Science, the University of Tokyo, as a Technical Associate in 1996, and was appointed as a Research Asso-

ciate in 2003. In 2005, he moved to Kobe University, Kobe, Japan. Since 2007, he has been an Associate Professor with the Department of Information Science at Kobe University. He is also a Collaborative Researcher with the Institute of Industrial Science, the University of Tokyo. His current research interests include low-voltage SRAM, RF circuits and ubiquitous sensor networks. Dr. Kawaguchi was a recipient of the IEEE ISSCC 2004 Takuo Sugano Outstanding Paper Award and the IEEE Kansai Section 2006 Gold Award. He has served as a Design and Implementation of Signal Processing Systems (DISPS) Technical Committee Member for the IEEE Signal Processing Society, as a Program Committee Member for the IEEE Custom Integrated Circuits Conference (CICC) and IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips) and as an Associate Editor of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and IPSJ Transactions on System LSI Design Methodology (TSLDM). He is a member of the IEEE, ACM, IEICE and IPSJ.

Koji Tsunoda received B.S. and M.S. degrees in Electronics Engineering from the University of Tokyo, Tokyo, Japan, in 1995 and 1997, respectively. In 1997, he joined Fujitsu Laboratories Ltd., Atsugi, Japan, where he was engaged in the research and development of embedded memory devices. He was also a visiting scholar at Stanford University, California, from 2005 to 2006. He received his Ph.D. in Electronics Engineering from Tohoku University, Sendai, Japan, in 2010. He joined the Low-power

Electronics Association & Project (LEAP) in 2010, and his present activities include the development of spin-transfer torque magnetoresistive RAM.

tron Device Society.

Toshihiro Sugii received B.S, M.S. and Ph.D. degrees in Electrical Engineering from Tokyo Institute of Technology in 1979, 1981 and 1991, respectively. In 1981, he joined Fujitsu Laboratories Ltd., Japan, where he was engaged in the development of CMOS devices. In 2010, he joined the Low-power Electronics Association & Project (LEAP), Japan, where he is directing a national project on STT-MRAM. Dr. Sugii is a fellow of the Japan Society of Applied Physics and a member of the IEEE Elec-