# 動的電圧制御環境下における 0.3-V 動作 64-kb SRAM

## A Vth-Variation-Tolerant 64-kb SRAM with 0.3-V Minimum Operation Voltage under DVS Environment

森田 泰弘<sup>\*1</sup> 藤原 英弘<sup>\*2</sup> 野口 紘希<sup>\*3</sup> 川上 健太郎<sup>\*2</sup> 宮越 純一<sup>\*2</sup>

Yasuhiro Morita Hidehiro Fujiwara Hiroki Noguchi Kentaro Kawakami Junichi Miyakoshi

三上 真司<sup>\*1</sup> 新居 浩二<sup>\*2</sup> 川口 博<sup>\*3</sup> 吉本 雅彦<sup>\*3</sup>

Shinji Mikami Koji Nii Hiroshi Kawaguchi Masahiko Yoshimoto

\*1 金沢大学大学院自然科学研究科

\*2 神戸大学大学院自然科学研究科

\*3 神戸大学工学部

Graduate School of Natural Science and Technology,

Kanazawa University

Graduate School of Science and Technology,

Kobe University

Faculty of Engineering,

Kobe University

### 1. はじめに

微細化の進展について SoC に内蔵する SRAM の規模が増大している。将来 LSI チップ面積の 90%以上を SRAM が占めると予測されており、SoC の低電力化には SRAM の低消費電力化が必要不可欠である。一方、携帯機器向け SoC の消費電力を削減する手法として、回路の動作周波数と電源電圧を動的に制御する DVS (Dynamic Voltage Scaling) が一般的に知られている [1]。しかしながら、微細化が進むにつれしきい値電圧 (Vth) のばらつきの影響により SRAM の低電圧動作が困難となり、DVS による電圧制御範囲が狭まることが懸念される。本稿では、DVS 環境下において SRAM を低電圧で動作させるための最適電圧制御手法を開発したので紹介する。また、ASPLA 90-nm プロセスにより 64-kb SRAM を試作し、本制御手法の有効性を確認したので報告する。

### 2. 最適電圧制御手法

#### 2.1 最適電圧制御手法の詳細

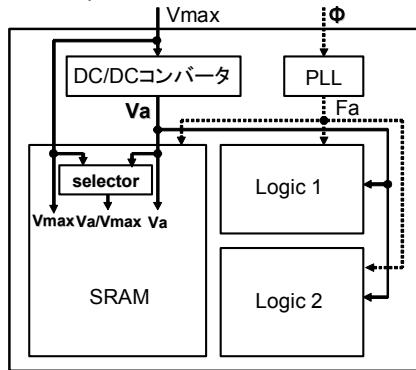

DVS 環境では、図 1 に示すように外部から一定の高電圧  $V_{max}$  が入力され、DC-DC コンバータなどで変換された動的制御電圧  $V_a$  が SoC 内の論理部及び SRAM に供給される。ここで、 $V_a$  は最低動作電圧  $V_{min}$  と  $V_{max}$  の間の電圧値である。本稿では、90-nm プロセスでの  $V_{max}$  を 1.0V とする。最適電圧制御手法では、SRAM に  $V_a$  及び  $V_{max}$  の 2 電源を供給し、メモリセルに印加する各電圧を読み出し/書き込み動作に応じて切り替えることにより、読み出し時、書き込み時それぞれの動作マージンを確保する。

表 1 に最適電圧制御手法の詳細を示す。読み出し時はメモリセルの電源電圧を  $V_{max}$  に設定し、読み出しマージンを最大化する。一方、書き込み時はメモリセルのワード線電圧を  $V_{max}$  に設定し、書き込みマージンを増大させる。また、pMOS 負荷トランジスタの基板バイアス電圧 ( $V_{bp}$ ) を常に  $V_{max}$  に設定する。書き込み時に  $V_a$  が  $V_{max}$  より低い場合、逆方向に基板バイアスが印加され pMOS のしきい値電圧が上昇し、書き込みマージンが拡大する。なお、 $V_{bp}$  が  $V_{max}$  を超えないため、GIDL (Gate-Induced Drain Leakage) 電流や NBTI (Negative Bias Temperature Instability) の問題は発生しない。また、本制御手法の実装にトリプルウェルプロセスを必要としないため、ソフトエラー耐性が強い、といった利点がある。

#### 2.2 動作マージンの改善効果

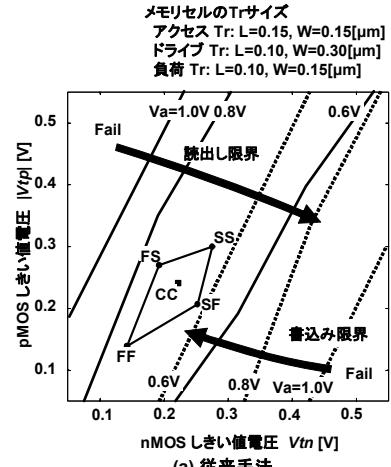

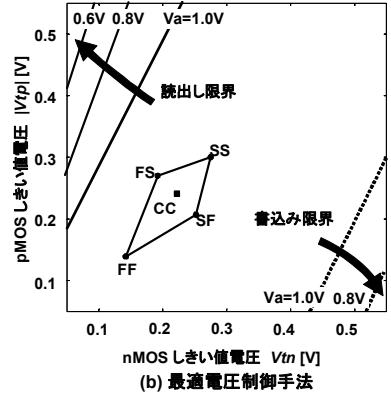

最適電圧制御手法による動作マージンの改善効果を、図 2 に示すミルキーウェイプロットで評価する。ミルキーウェイプロットはシミュレーションにより導出され、 $V_{th}$  ばらつきに関しては、グローバルばらつきは  $3\sigma$ 、ローカルば

らつきは  $6\sigma$  まで考慮されている。SRAM セルが安定に動作するためには、プロセスコーナー (FF, FS, SF, SS) が読み出し限界と書き込み限界で挟まれた正常動作領域に収まる必要がある。従来の SRAM では、図 2 (a) のように  $V_a$  が低下するにつれて正常動作領域が狭くなるが、提案手法では図 2 (b) のように  $V_a$  の低下にかかわらず正常動作領域が広く、動作マージンが十分に確保されることがわかる。

#### 2.3 回路設計

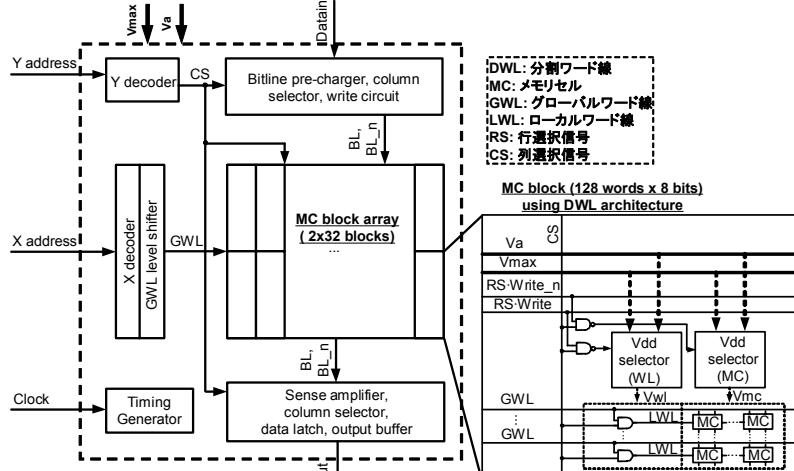

図 3 に最適電圧制御手法を適用した 64-kb SRAM の回路図を示す。メモリセルアレイは 128 words x 8 bits から成るメモリセルブロックに分割され、メモリセルブロックごとに電圧制御が行われる。最適電圧制御手法を適用するに当たり導入した回路は、各メモリセルブロックに備わったメモリセルの電源電圧 ( $V_{mc}$ ) 及びワード線電圧 ( $V_{wl}$ ) を制御するための電源セレクタ、及び書き込み時にワード線を  $V_{max}$  に立上るためのレベルシフタである。また、メモリセルブロックごとにワード線を分割する分割ワード線構造 (DWL) [2] を採用し、非選択ブロックの保持データがワード線の立上りによって破壊されるのを防止する。提案 SRAM では、アクセストランジスタのチャネル長を最小の  $0.10 \mu m$  ではなく  $0.15 \mu m$  として読み出しマージンを改善し、またビット線リーケークを削減する。これによる性能のオーバーヘッドはごくわずかである。

#### 3. 測定結果

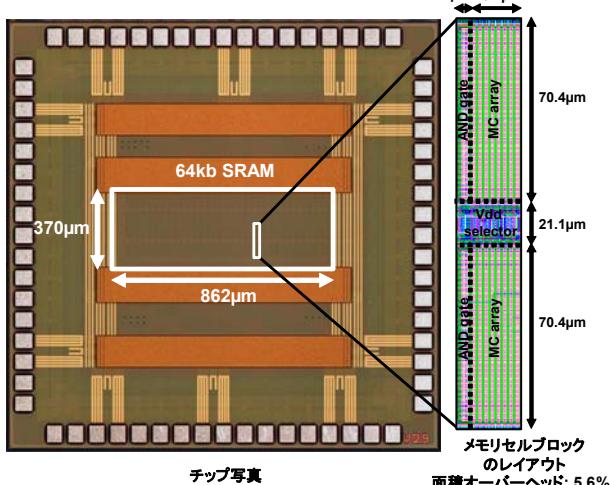

ASPLA 90-nm プロセスにより 64-kb SRAM を試作し、評価を行った。図 4 にチップ写真及びメモリセルブロックのレイアウトを示す。提案手法による面積オーバーヘッドは 5.6% であり、主に電源セレクタとレベルシフタによる。

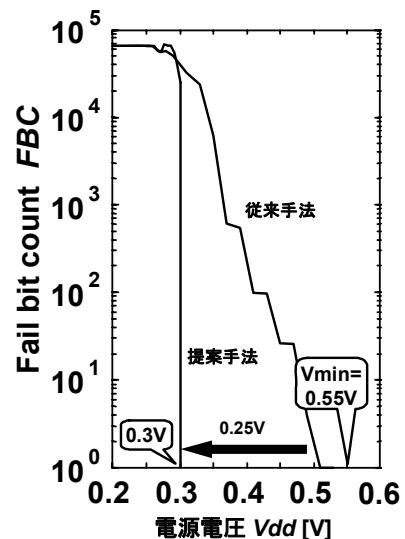

動作マージンの改善効果を表現するものとして、図 5 に SRAM のフェイルビットカウントの  $V_{dd}$  依存性を示す。フェイルビットカウントの実測では、クロックのサイクルタイムを  $1 \mu s$  とした。CC プロセスコーナーにおいて、従来手法ではメモリセルにおける  $V_{th}$  ばらつきにより  $V_{min}$  が  $0.55 V$  であるが、提案手法により  $V_{min}$  が  $0.3 V$  となる。なお、提案手法では図 1 により  $V_a$  が低下してもメモリセルの動作マージンが十分確保されているため、 $V_{min} = 0.3 V$  となる要因は周辺回路にある。最適電圧制御手法により  $V_{min}$  を  $0.25 V$  引き下げることが可能なため、DVS により消費電力を削減する見通しが立った。

#### 4. 結論

DVS 環境下において SRAM の低電圧動作を実現するための最適電圧制御手法を提案した。ASPLA 90-nm プロセスにより 64-kb SRAM を試作し、評価を行った結果、最適電圧制御手法により  $0.3 V$  の低電圧動作が可能であることを実証した。

## 参考文献

- [1] H. Ohira, et al., "A feed-forward dynamic voltage control algorithm for low power MPEG4 on multi-regulated voltage CPU," IEICE Trans. Electron., Vol.E87-C, No.4, pp.457-465, Apr. 2004.

- [2] M. Yoshimoto, et al., "A divided word-line structure in the static RAM and its application to a 64K full CMOS RAM," IEEE J. Solid-State Circuits, Vol.18, No.5, pp.479-485, Oct. 1983.

図 1 DVS の概略図

図 3 64-kb SRAM のブロック図

図 4 チップ写真及びメモリセルブロックのレイアウト

## 謝辞

本チップ試作は東京大学大規模集積システム設計教育研究センターを通じ株式会社半導体理工学研究センター、富士通株式会社、松下電器産業株式会社、NEC エレクトロニクス株式会社、株式会社ルネサステクノロジ、株式会社東芝の協力で行われたものである。試作チップの評価に関して、京都大学の小林和淑助教授ならびに京都大学 VDEC サブセンターに深謝します。

表 1 最適電圧制御手法の詳細

| State Part  | 従来手法 | 最適電圧制御手法 |      |      |

|-------------|------|----------|------|------|

|             |      | 読み出し     | 書き込み | 非選択  |

| 周辺回路の Vdd   | Va   | Va       | Va   | Va   |

| BL プリチャージ電圧 | Va   | Va       | Va   | Va   |

| WL 電圧       | Va   | Va       | Vmax | -    |

| MC Vdd      | Va   | Vmax     | Va   | Va   |

| MC Vbp      | Va   | Vmax     | Vmax | Vmax |

Vmax: 最大電圧

Va: 動的制御電圧

メモリセルの Tr サイズ

アクセス Tr: L=0.15, W=0.15[μm]

ドライブ Tr: L=0.10, W=0.30[μm]

負荷 Tr: L=0.10, W=0.15[μm]

(a) 従来手法

(b) 最適電圧制御手法

図 2 ミルキー ウェイ プロット

図 5 フェイルビットカウントの Vdd 依存性