# センサノードの製造バラツキを考慮した ネットワーク可用時間改善の一検討

Long-lived network by considering production tolerance of sensor node

|                                       |                                       |                                    |                                         |                                  |

|---------------------------------------|---------------------------------------|------------------------------------|-----------------------------------------|----------------------------------|

| 芳野宏徳 <sup>1</sup><br>Hironori Yoshino | 青西孝文 <sup>1</sup><br>Takafumi Aonishi | 一圓真澄 <sup>1</sup><br>Masumi Ichien | 松田隆志 <sup>1</sup><br>Takashi Matsuda    | 太田能 <sup>2</sup><br>Chikara Ohta |

|                                       | 川口博 <sup>2</sup><br>Hiroshi Kawaguchi |                                    | 吉本雅彦 <sup>2</sup><br>Masahiko Yoshimoto |                                  |

|                                                                                         |                                                                  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 神戸大学 自然科学研究科 <sup>1</sup><br>Graduate School of Science and Technology, Kobe University | 神戸大学 工学部 <sup>2</sup><br>Faculty of Engineering, Kobe University |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|

## 1 はじめに

近年注目されているセンサネットワークでは、各ノードをいかに低消費電力で駆動して寿命を延ばし、ネットワークを維持するか、が大きな課題となっている。

ノード内のプロセッサを低電力化するには、一般にはプロセッサへの印加電圧  $V_{dd}$  を動作可能な範囲で下げればよい。従来研究では、プロセッサへの印加電圧  $V_{dd}$  は一定であると仮定している。しかしながら実際には、製造工程で出る誤差から動作可能な印加電圧にはばらつきが発生する[1]。この結果、各センサノードは、同じ容量をもつ電池で駆動されても異なる稼動時間を持つことになる。

本稿では、このばらつきを考慮して、DC-DC コンバータによりプロセッサへの印加電圧を制御することで、センサネットワークの可用時間が改善されることを示す。さらにプロセッサの製造ばらつきを考慮してノード配置をおこなうことにより、センサネットワークの可用時間をさらに改善できることを示す。

## 2 性能バラツキのモデル化

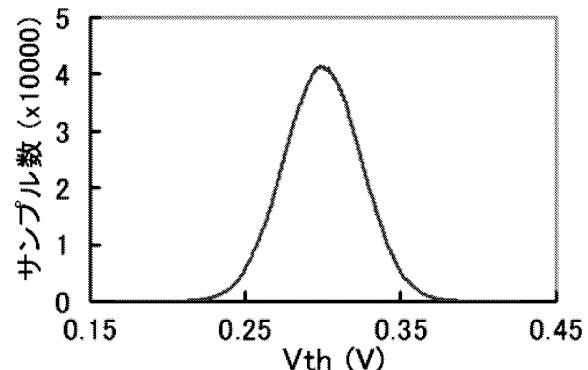

製造工程での系統誤差により、プロセッサ間で、内部のトランジスタのしきい値電圧 ( $V_{th}$ ) の平均値にバラツキが発生する。文献[2]によれば、製造バラツキから、チップの平均  $V_{th}$  は、標準偏差  $\sigma_{vth} = 0.025V$  の正規分布に従うバラツキがあると推定できる(図1)。動作周波数  $f$  は式(1)で決定される[1]。ここで、 $K$  は定数であり、 $\alpha$  はデバイス世代に応じて 1 から 2 の値を取る。

$$f = \frac{(V_{dd} - V_{th})^\alpha}{V_{dd}} K \quad (1)$$

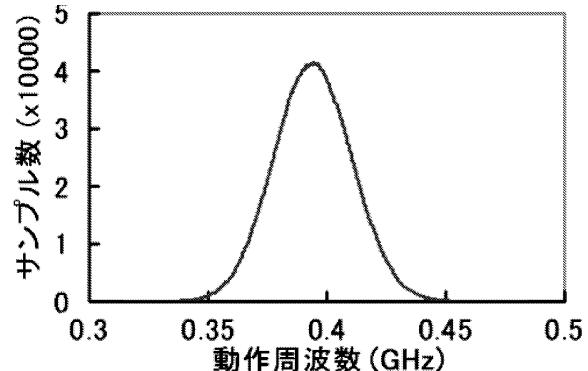

同じ製造工程のセンサノード用のプロセッサ ( $\mu_{vth} = 0.3V$ ,  $V_{dd} = 1.2V$ ,  $\alpha = 1.5$ , 論理段数 3 倍 :  $K/3$ ) の周波数を試算すると、中心値  $\mu_f = 394MHz$ , 標準偏差  $\sigma_f = 16MHz$  のバラツキを示した(図2)。

## 3 ノードの平均寿命の延長方法

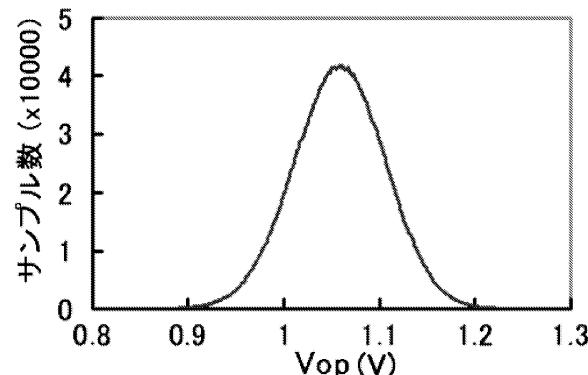

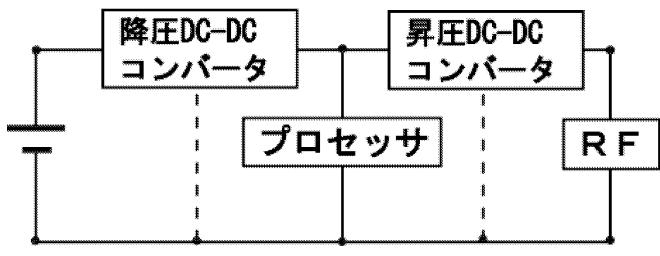

式(1)より、周波数を低い基準 ( $F_{base} = \mu_f - 3\sigma_f = 0.345$ ) で一定にした場合、動作電圧  $V_{op}$  が基準値 (1.2V) よりも低い値でばらつく(図3)。DC-DC コンバータ[1]を用いて、この  $V_{op}$  に合わせて電源電圧を下げれば、低電力化が見込める。さらに、RF 回路はプロ

図 1 しきい値電圧のバラツキ

図 2 動作電圧を一定とした場合の動作周波数の分布

図 3 動作周波数を一定とした場合の動作電圧の分布

セッサ回路に比べて動作電圧が高くバラツキが小さいため、昇圧 DC-DC コンバータ[4]を用いることで(図4),

電力消費の効率化を図る。

図 4 回路モデル

#### 4 製造バラツキを考慮したノード配置方法

全てのノードが一つの基地局端末にデータを集めるアプリケーションを考える。基地局に近い程、通信が多く消費が大きいと考えられるため、基地局からの距離が近い順に、低消費ノードを配置することができれば、ネットワークの可用時間は延びると考えられる。

#### 5 シミュレーション

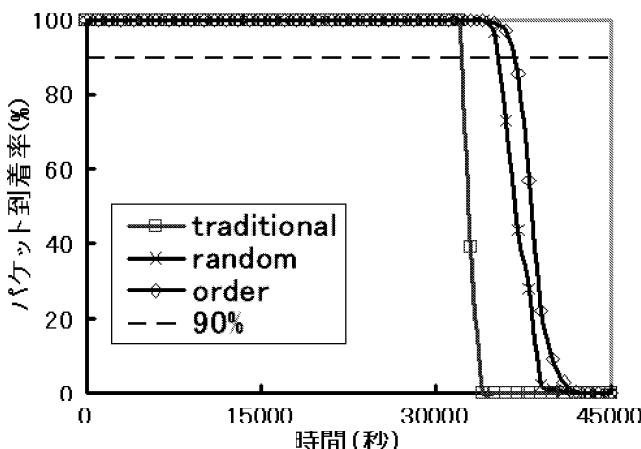

100m×100m のフィールドの中に、256 個のノードを格子状に配置する。ノードは周期的に sleep 状態と通常状態を繰り返す。通信前に、preamble を一定時間送信し、周囲のノードの通信を停止させることで通信の衝突を防ぐ。ルーティングプロトコルは tiny diffusion[3] を用いる。一定電圧(1.2V)で動かす従来のケース (traditional), ばらついたままランダムに配置したケース (random), 基地局からの距離順に低電圧動作ノードを配置したケース (order) を比較する。traditional に比べ、random は約 10 % の改善が見られる。order は、traditional に比べ約 14 % の改善が見られた (図 5)。

図 5 ネットワーク可用時間

#### 6 むすび

製造バラツキをもとに低電圧化をおこない、さらにノード配置を工夫することによって、ネットワーク可用時間を改善できることを示した。

#### 謝辞

本研究の一部は、平成 17 年度文部科学省科学研究費補助金若手研究 (B) (課題番号 16700066 ならびに 16760271) および平成 16 年度柏森情報科学振興財団研

究助成 (課題番号 K16 研 IX 第 183 号) によりおこなわれた。

#### 参考文献

- [1] 桜井貴康 他, “低消費電力, 高速 LSI 技術,” 株式会社アライズ社, Oct. 1998.

- [2] J. Tschanz, J. T. Kao, S. G. Narendra, R. Nair, D. A. Antoniadis, A. P. Chandrakasan, V. De, “Adaptive Body Bias for Reducing Impacts of Die-to-die and Within-die Parameter Variations on Microprocessor Frequency and Leakage,” IEEE J. Solid-State-Circuits, vol.37, no.11, Nov. 2002.

- [3] E. Osterweil and D. Estrin, “Tiny Diffusion in the Extensible Sensing System at the James Reserve,” <http://www.cens.ucla.edu/~eoster/tinydiff/>, May 2003.

- [4] Y. Yoshida, F. Utsunomiya, and T. Douseki, “Sub-1-V Power-Supply System with Variable-Stage SC-Type DC-DC Converter Scheme for Ambient Energy Sources,” IEICE Trans. Electron., vol.E88-C, no.4, April 2005.