# ビット線電力を 8 割削減する動画像処理応用 10T 非プリチャージ 2-port SRAM

A 10T Non-Precharge Two-Port SRAM for 74% Power Reduction in Video Processing

井口友輔<sup>\*1</sup> 野口紘希<sup>\*1</sup> 藤原英弘<sup>\*1</sup> 森田泰弘<sup>\*1</sup> 新居浩二<sup>\*1,\*2</sup> 川口博<sup>\*1</sup> 吉本雅彦<sup>\*1</sup>

Yusuke Iguchi H.Noguchi H.Fujiwara Y.Morita K.Nii H.Kawaguchi M.Yoshimoto

\*1 神戸大学

Kobe University

\*2 ルネサステクノロジ

Renesas Technology Corp

## 1. はじめに

H.264 などの実時間動画像処理プロセッサにおいて、フレームバッファや再構成画像メモリとして大容量の SRAM が使用されている。このような動画像処理プロセッサの低電力化には SRAM の低消費電力化が必要不可欠である。本稿では、読み出しビット線の充放電電力を削減するためにビット線非プリチャージ方式の 10Tr 構成メモリセルを開発し、本メモリセルで構成された SRAM(以下 10T SRAM)を動画像処理バッファに使用した際の読み出しビット線電力削減効果を見積もったので報告する。

## 2. 10T 非プリチャージ メモリセル

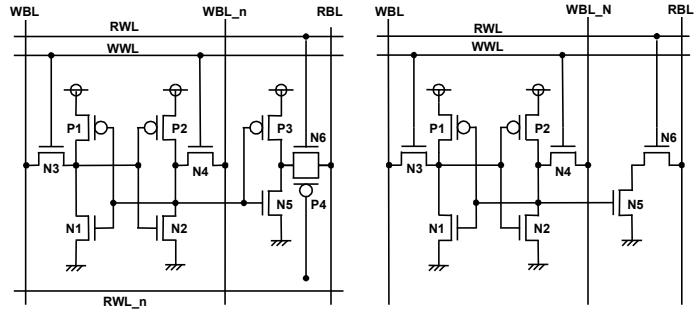

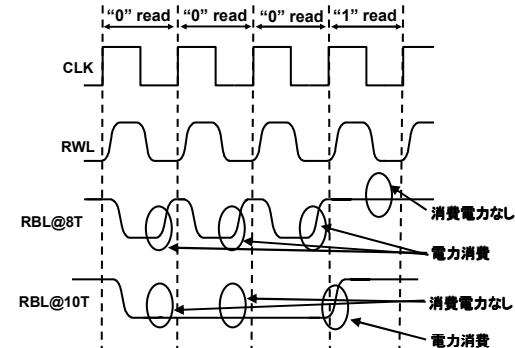

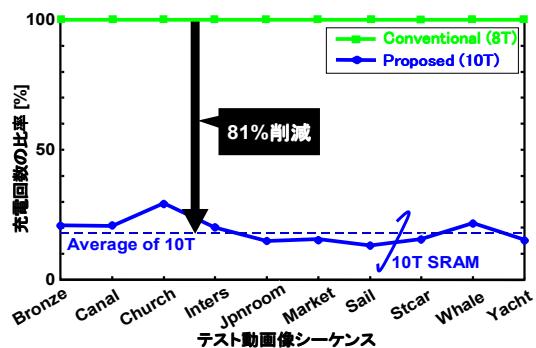

図 1 に 10T メモリセル及び、8T メモリセルの回路図を示す。従来の 8T メモリセルはビット線プリチャージ方式であり、"0" を読み出されるたびに読み出しが動作で放電された電荷がプリチャージされるため、読み出しビット線の充放電電力が発生する。そこで、提案する 10T メモリセルでは、メモリセル内にプリチャージ動作をする回路を組み込むことにより、メモリセル独自で読み出しビット線の充放電を可能にした。これにより、従来手法におけるプリチャージを必要としないため、"1" 読出しのあと "0" 読出しのときにのみ放電し、"0" 読出しのあと "1" 読出しのとき、充電電力が発生する。また、画像では、隣接する画素同士に強い相関性が存在するため、隣接するデータの相関性を利用して適切にマッピングすることで読み出しだけの変化を減少させることができる。図 3 に 10 種類の HDTV 解像度のテスト動画像シーケンス (Bronze, Canal, Church, Intersection, Japanese Room, Market, Yachting, Street Car, Whale, Yacht) から H.264 符号化によって生成された再構成画像における充電回数削減効果を示す。8T SRAM と比較して、読み出しが動作時の充電回数を平均 81% 削減させることができる。

また、プリチャージ期間がないため、従来 SRAM と比較すると、高速に動作させることができ、同じ周波数で動作させた場合、電源電圧を下げることができる。さらに低消費電力化を行うことができる。

## 3. 結論

読み出しビット線の充放電電力を削減するためにビット線非プリチャージ方式の 2-port 10T SRAM を提案する。結果、提案する SRAM を H.264 で符号化された再構成画像に用いることで、2-port 8T SRAM と比較し、ビット線電力を 8 割削減することができる。

図 1. 2-port メモリセル回路図

図 2. 動作波形

図 3. 充電回数削減効果