# VLSI 設計における Dual $V_{DD}$ 回路の電力削減効果

## Power reduction effect of dual $V_{DD}$ circuits in VLSI design

徳永和宏 川口博 桜井貴康

Kazuhiro Tokunaga Hiroshi Kawaguchi Takayasu Sakurai

東京大学 生産技術研究所

Institute of Industrial Science, The University of Tokyo

### 1. はじめに

近年、携帯電話、ノート PC、PDA 等の携帯機器の需要の増加に伴い VLSI 設計における低消費電力化が求められている。VLSI の論理合成において、ノン・クリティカルパスの遅延はクリティカルパスの遅延より余裕（スラック）があるため、ノン・クリティカルパスでは低消費電力セルを使用することができる[1]。この場合、セル・ライブラリには高速・高消費電力なセルから低速・低消費電力なセルまでいくつかの種類が必要になる[2]。しかし、電源電圧  $V_{DD}$  が異なるセルを用いて回路（以下、2 つの電源電圧の場合 Dual  $V_{DD}$  回路と呼ぶ）を実装するためには Clustered Voltage Scaling (CVS) 手法[3]を用いて設計しなければならない。本稿では CVS 手法を考慮した Dual  $V_{DD}$  回路の電力削減効果について述べる。

### 2. CVS dual $V_{DD}$ 回路の論理合成

本稿では産業用ライブラリから論理合成に必要な 20 個のセルを取り出し、これを High  $V_{DD}$  ライブラリとしている[4]。また、この High  $V_{DD}$  ライブラリを元に電源電圧  $V_{DD}$  を 0.7 倍にしてシミュレーションにより特徴化したライブラリを Low  $V_{DD}$  ライブラリとしている。ライブラリの生成にはライブラリ生成ツールの Library compiler, Synopsys を用いる。そして、生成した Low  $V_{DD}$  ライブラリと High  $V_{DD}$  ライブラリの両方を用いて論理合成ツール Design compiler, Synopsys 上で CVS 手法を考慮した Dual  $V_{DD}$  回路を論理合成する。

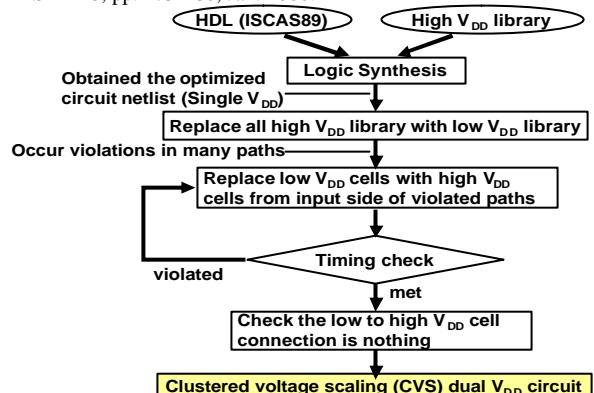

本稿では、回路の機能を記述した Hardware Description Language (HDL) にベンチマーク回路セットの ISCAS89 を用いることとする。論理合成における CVS 手法を考慮した Dual  $V_{DD}$  回路合成のための流れ図を図 1 に示す。

### 3. 結果とまとめ

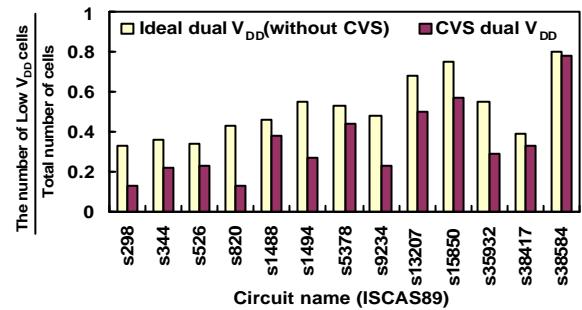

図 2 に各回路でのセルの総数に占める Low  $V_{DD}$  ライブラリ・セルの使用数の割合を示す。理想的な (CVS を考慮しない) Dual  $V_{DD}$  回路では Low  $V_{DD}$  セルの使用率がセル全体の 51% であったのに対し、CVS を考慮した Dual  $V_{DD}$  回路では Low  $V_{DD}$  セルの使用率がセル全体の 34% となった。

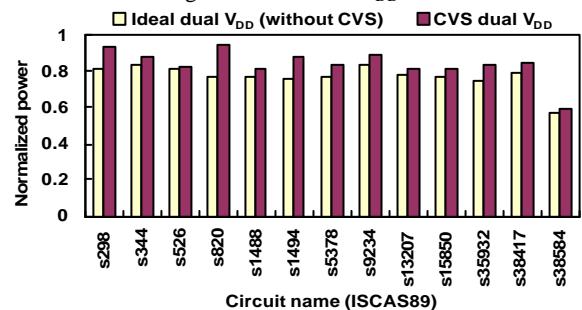

図 3 に理想的な Dual  $V_{DD}$  回路と CVS を考慮した Dual  $V_{DD}$  回路の消費電力を示す。理想的な Dual  $V_{DD}$  回路では Single  $V_{DD}$  回路 (High  $V_{DD}$  のみの回路) の平均で 77% の消費電力となり、CVS を考慮した Dual  $V_{DD}$  の回路では Single  $V_{DD}$  の回路の平均で 84% の消費電力となることが分かった。従って、CVS 手法を考慮すると Dual  $V_{DD}$  回路の電力削減は理想的な Dual  $V_{DD}$  回路の 68% となることが分かった。

### 参考文献

- [1] M. Hamada, Y. Ootaguro, and T. Kuroda, "Utilizing Surplus Timing for Power Reduction," in Proc. of CICC2001, pp.89-92, May. 2001.

- [2] 徳永和宏, 宮崎隆行, 桜井貴康, "低電力・ライブラリ・セルの選択に関する一検討," IEICE ソサイエティ大会, A-3-8, Sep. 2003.

- [3] K. Usami, and M. Horowitz, "Clustered voltage scaling technique for low-power design," ACM/IEEE ISLPD95, pp. 3-8, April. 1995.

- [4] N. Duc, and T. Sakurai, "Compact yet High-Performance (CyHP) Library for Short Time-to-Market with New Technologies," ASPDAC, pp. 475-480, Jan. 2000.

Fig. 1. CVS realization flow (Design compiler, Synopsys)

Fig. 2. Ratio of low  $V_{DD}$  cells

Fig. 3. Power consumption