# ビット線充放電電力を 53%削減する動画像処理応用 2-port SRAM

A Two-port SRAM for Real-Time Video Processor Saving 53% of Bitline Power with Majority Logic and Data-Bit Reordering

藤原 英弘<sup>\*1</sup> 新居 浩二<sup>\*1</sup> 宮越 純一<sup>\*1</sup> 村地 勇一郎<sup>\*1</sup> 野口 紘希<sup>\*1</sup> 森田 泰弘<sup>\*2</sup> 川口 博<sup>\*3</sup> 吉本 雅彦<sup>\*3</sup> Hidehiro Fujiwara K. Nii J. Miyakoshi Y. Murachi H. Noguchi Y. Morita H. Kawaguchi M. Yoshimoto

\*1 神戸大学大学院自然科学研究科

Graduate School of Science and Technology,

Kobe University

\*2 金沢大学大学院自然科学研究科 Graduate School of Natural Science and Technology, Kanazawa University \*3 神戸大学工学部 Faculty of Enginnering, Kobe Univertiy

## 1. はじめに

大容量 SRAM が H.264 などの実時間動画像処理プロセッサにおけるフレームバッファや再構成画像メモリとして用いられている.このような動画像処理プロセッサの低電力化には SRAM の低消費電力化が必要不可欠である.本稿では,画像の持つ隣接画素の相関性に着目し,多数決論理とReordering 処理を用いることにより,画像処理に適した 2-portSRAM のビット線充放電電力を 53%削減することができる手法を開発した.

### 2. 多数決論理 SRAM

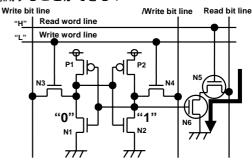

2-port SRAM のメモリセル回路を図 1 に示す. "0"読出し時には,読出し用トランジスタ N6 がオン状態となるので,ビット線充放電電力が発生する.一方、"1"読出し時には,N6 がオフ状態となるので,ビット線充放電電力は発生しない.よって,"0"読出しの数を削減し"1"読出しの数を増加させれば,ビット線充放電電力を削減することができる.

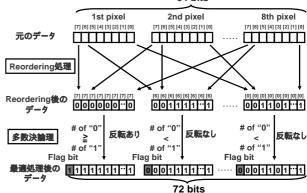

書込み動作時に、"1"が多く書込まれるようにするため,多数決論理判定回路を用いて、"0"の個数が"1"の個数よりも多い場合に書込みデータを反転する。また、書込みデータが反転したかどうかの情報を、フラグビットとして付加する。読出し動作時にフラグビットが"1"の場合、データ反転を行うことにより元のデータを復元する。同時に読み書きするデータが8bitの場合、入力データがランダムパターンだと仮定すれば、多数決論理を用いることにより、ビット線充放電電力を18%削減することができる。

## 3. Reordering 処理

画像では,隣接する画素同士に強い相関性が存在する。 また,画素データの上位ビットほど相関性は大きく,下位 ビットほど相関性は小さくなる.この性質を利用して,図 2 に示すように,書込み動作時に,隣接する横8 画素のデ ータをビットごとのグループに並べ替える Reordering 処理 を行う. Reordering 処理により,上位ビットのグループは 全て"1"か、全て"0"に偏る可能性が大きくなる、この Reordering 処理を行った後に多数決論理を用いることで, より効率的に"0"書込みの個数を削減することができる. 図 3 は , 10 種類の HDTV 解像度のテスト動画像シーケン ス (Bronze with Credit, Building along the Canal, Church, Intersection, Japanese Room, European Market, Yachting, Street Car, Whale Show, Yacht Harbor) から H.264 符号化によって 生成された再構成画像に,多数決論理と Reordering 処理を 用いる場合のビット線充放電電力の削減効果を示す、ビッ ト線充放電電力を平均53%削減することができる.

#### 4. 結論

画像の持つ隣接画素の相関性に着目し,2-port SRAM に多数決論理と Reordering 処理を用いる手法を提案した. H.264 符号化によって生成された再構成画像に,本提案手法を適用することにより,SRAM のビット線充放電電力を53%削減することができる.

図1.2-port SRAM のビット線の充放電 64 bits

図 2 . Reordering 処理と多数決論理

100

| 53% 削減

| 平均充放電電力

Bronze Canal Church Inters Jpnroom Market Yachting Stcar Whale Harbor

テスト動画像シーケンスの種類 図3.消費電力削減効果