製造ばらつきを考慮したセンサネットワークノード消費電力モデルの提案と評価

芳野

宏徳<sup>†</sup>

竹内

隆<sup>†</sup>

一圓

真澄<sup>†</sup>

松田

隆志<sup>†</sup>

三上

真司<sup>††</sup>

太田

能<sup>†††</sup>

川口

博<sup>†††</sup>

吉本

雅彦<sup>†††</sup>

†神戸大学大学院 自然科学研究科 情報知能工学専攻 〒657-8501 兵庫県神戸市灘区六甲台町 1-1 ††金沢大学大学院 自然科学研究科 電子情報科学専攻 〒920-1192 石川県金沢市角間 †††神戸大学 工学部 情報知能工学科

E-mail: † take@cs28.cs.kobe-u.ac.jp

あらまし ワイヤレスセンサネットワークでは、ライフタイムの拡大が最も重要な課題である。ネットワークのライフタイムを拡大するためには、システム全体の最適設計をしなければならない。設計したシステムを評価するために、シミュレータに実装可能なセンサノードの消費電力モデルが求められていた。本研究では、センサノードの消費電力モデルに、現在CMOS回路で問題となっている関値電圧の製造ばらつきを導入した。従来モデルと比較すると、関値電圧ばらつきを考慮した場合、消費電力がばらつき、平均消費電力が増大することが判明した。さらに、ネットワークシミュレータに実装し、ネットワークレベルで比較した。その結果、従来のモデルはばらつきのあるモデルよりもシステムライフタイムを長く見積もる傾向にあることがわかった。

キーワード ワイヤレスセンサネットワーク、閾値電圧ばらつき、消費電力モデル

# Impact of Node Power Variation against Life Time of Sensor Networks

Hironori Yoshino<sup>†</sup> Takashi Takeuchi<sup>†</sup> Masumi Ichien<sup>†</sup> Takashi Matsuda<sup>†</sup> Shinji Mikami<sup>††</sup> Hiroshi Kawaguchi<sup>†††</sup> Chikara Ohta<sup>†††</sup> and Masahiko Yoshimoto<sup>†††</sup> † Graduate School of Science and Technology, Kobe University, 1-1 Rokkodai, Nada, Kobe, 657-8501 †† Graduate School of Natural Science and Technology, Kanazawa University, Kakuma, Kanazawa, 920-1192 ††† Faculty of Engineering, Kobe University, 1-1 Rokkodai, Nada, Kobe, 657-8501

E-mail: † take@cs28.cs.kobe-u.ac.jp

**Abstract** We introduced manufacturing variation into a power model for a wireless sensor network node. Network protocols for wireless sensor networks such as media access control and routing should be evaluated in terms of life time as a whole system. In fact, there exists variation in power node-by-node due to the manufacturing variation. In the previous research, however, this effect has not been investigated at all since it has been supposed that all nodes have the same power. In this paper, we develop a more exact power model for sensor nodes, which we name the threshold-voltage variation model, considering threshold-voltage variation in a manufacturing process. A microprocessor and RF part are considered as hardware blocks in the model, which is then implemented to QualNet in order to evaluate the impact on the life time. The simulation results show that the conventional model overestimates the life time longer than our model.

Keyword Wireless sensor network, Threshold-voltage variation, Power mode

# I. Introduction

In wireless sensor networks (WSNs), expansion of available time, i.e. life time, is one of the most important subjects. Network protocols for WSNs such as media access control and routing should be evaluated in terms of life time in a whole network system. Therefore, many researchers have implemented their proposed protocols into network simulators such as NS-2 and QualNet [1-2]. In their studies, every node has the same power performance. However in fact, there exists variation in power node-by-node due to manufacturing variation, where only a few nodes with high power consumption may shorten the network life time. To the best of our knowledge, however, this aspect has not been addressed at all.

Process, voltage, and temperature (PVT) are major factors of variation in CMOS VLSI process. The process variation is called a manufacturing variation, which is twofold: systematic variation, and random variation. Although both variations take the form of a threshold-voltage variation, behaviors are different. The random variation appears as a transistor-by-transistor variation while the

systematic one is observed as a chip-by-chip variation. The random variation is mitigated in a chip power since millions transistors are distributed on a chip. In this paper, therefore, we consider only the systematic variation as a first step. To the best of our knowledge, scientific data about threshold-voltage variation in a latest CMOS process technology has not been published.

In this paper, we address the effect of power variation of nodes on system-level performance, i.e. network life time. First, we develop a power model for a node considering threshold-voltage variation in a microprocessor and RF (radio frequency) part, which we call the threshold-voltage variation (TV) model. We then implement the model into QualNet, which is one of network simulators, and evaluate the effect of the power variation on network life time.

The rest of the paper is organized as follows: In Section II, we show a typical architecture of sensor node. In Section III, we build a model of threshold-voltage variation based on variation of an operating frequency in an Intel microprocessor. In Section VI, we describe power variation in the node chip compared with the conventional threshold-voltage constant (TC) model. In Section V,

we exhibit a result of network simulation. Finally, we conclude the paper in Section VI.

## II. SENSOR NODE ARCHITECTURE AND POWER COMPONENTS

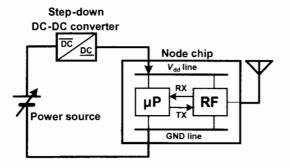

Fig. 1 shows a typical schematic of a sensor node. A small battery, solar cell, or even energy scavenging such as vibration energy [3] is utilized as a power source, and thus its output voltage is not unregulated. The step-down DC-DC converter in the figure regulates the output voltage of the power source to a lower one, which is supplied to a node chip as a rated supply voltage ( $V_{\rm dd}$ ). If the output voltage of the power source becomes lower than  $V_{\rm dd}$ , the node chip goes down since the step-down DC-DC converter cannot compensate the negative voltage gap. A node chip is generally comprised of two blocks; a microprocessor and RF part. An RF part receives/transmits data and control packets from/to other sensor nodes by means of radio waves, and a microprocessor process them.

The node chip actually has power variation derived from threshold-voltage variation, and thus a life time of the sensor node is strictly varied node-by-node. In this paper, the impact against the life time in the sensor nodes caused by the power variation is described. Note that an energy variation in the power source is not considered, but if its variation is known, a similar analysis can be carried out.

Fig. 1. A typical sensor node. μP signifies a microprocessor.

A power in the node chip,  $P_{\text{node}}$ , is given as follows:

$$P_{\text{node}} = (P_{\mu P} + P_{RF}) / K_{\text{DCDC}}, \qquad (1)$$

where  $P_{\mu P}$  and  $P_{RF}$  are powers of a microprocessor and RF part, respectively.  $K_{DCDC}$  is an efficiency of a DC-DC converter, and achieves more than 90%[4].

## A. Power in Microprocessor

In a CMOS digital circuit, a switching delay,  $T_{\rm p}$ , is briefly expressed as a time to take a gate capacitance,  $C_{\rm L}$ , to be charged/discharged by a transistor on-current,  $I_{\rm on}$ . When there are n logic gates serially connected in a critical path, the maximum operating frequency,  $f_{\rm max}$ , is given as follows:

$$f_{\text{max}} \propto \frac{1}{nT_{\text{p}}} = \frac{I_{on}}{nQ_{\text{L}}} = \frac{(V_{\text{dd}} - V_{\text{th}})^{\alpha}}{nC_{\text{L}}V_{\text{dd}}}$$

$$= K_{\text{L}} \frac{(V_{\text{dd}} - V_{\text{th}})^{1.5}}{nV_{\text{dd}}},$$

(2)

where  $I_{\rm on}=(V_{\rm dd}-V_{\rm th})^{\alpha}$  and  $\alpha$  is a velocity saturation index [5]. If  $\alpha=2$ , it is said that  $I_{\rm on}$  is based on the classic Shockley model, however in a scaled process technology,  $\alpha$  is lowered and set to 1.5 in this paper [6]. A rated operating frequency,  $f_{\rm op}$ , must be lower than  $f_{\rm max}$ .

Power consumed in a digital circuit is comprised of two components. A power in a microprocessor,  $P_{\mu P}$ , includes a dynamic power,  $P_{\text{dyn}}$ , and subthreshold-leakage power,  $P_{\text{leak}}$ , as well.

## 1) Dynamic power

$P_{\text{dyn}}$  is a charge/discharge power along with transistor switching,

which is proportional to  $f_{\rm op}$ , and the square of  $V_{\rm dd}$  [7].

$$P_{\rm dvn} = K_2 f_{\rm op} C_{\rm L} V_{\rm dd}^2 \,. \tag{3}$$

# 2) Subthreshold-leakage power

Even when a transistor is in a subthreshold region, a subthreshold-leakage current flows through the transistor, which is  $P_{\text{leak}}$ .  $P_{\text{leak}}$  results in larger one as  $V_{\text{th}}$  becomes lower [7]:

$$P_{\text{leak}} = K_3 V_{\text{dd}} 10^{-V_{\text{th}}/S} , (4)$$

where S is a subthreshold swing, which is about 0.1 V/decade in a recent process technology. This implies that a subthreshold-leakage current goes up to ten times when  $V_{\rm th}$  is reduced by 0.1 V.

### B. Power in RF Part

In the RF part, transistors are biased to an intermediate voltage by a bias circuit, which always draws a bias current in an analog circuit. The biased transistor is usually in a saturation region, and the bias current is unfortunately dominant.

In an analog-circuit design, long-channel transistors are utilized to avoid the channel-length modulation effect and obtain the ideal saturation characteristics. A power in the RF part is represented as follows [8]:

$$P_{RF} = \beta V_{dd} (V_{gs} - V_{th})^{\alpha}$$

$$= \beta V_{dd} (V_{gs} - V_{th})^{2},$$

(5)

where  $\beta$  is a current amplification factor.  $\alpha$  is set to two since a long-channel transistor is used in the analog-circuit design, while it was 1.5 in the digital circuit as previously mentioned.

#### III. THRESHOLD-VOLTAGE VARIATION MODEL

In every chip, doping concentration and oxide thickness are different due to manufacturing variation, which basically causes the threshold-voltage variation.

# Threshold-Voltage Variation in Intel High- Performance μP

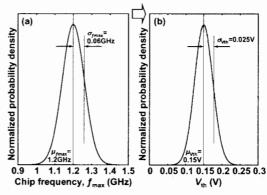

A distribution of chip frequencies in Intel high-performance microprocessors, which are determined by critical-path delays, was reported [9]. Fig. (a) is the distribution of the chip frequency. From this, we can conjecture the threshold-voltage variation as the systematic variation.

Fig. 2. Chip frequency distribution in Intel microprocessors, and its estimated distribution of threshold voltage.

Using (2), the threshold-voltage variation can be estimated as follows:

$$V_{\rm th} = V_{\rm dd} - 1.5 \frac{n f_{\rm max} V_{\rm dd}}{K_1} \ . \tag{6}$$

As the design parameters of the Intel microprocessor, we set  $V_{\rm dd}$  and  $\mu_{\rm Vth}$  to 0.9 V and 0.15 V, respectively. The critical path has 14 logic gates (n=14). Therefore, the constant,  $K_1$ , is 23.3×10<sup>6</sup> in (6). Fig.

(b) is the estimated distribution of the threshold voltage. The standard deviation of the threshold voltage in the Intel microprocessor,  $\sigma_{Vth}$ , is 0.025 V.

# 2) Threshold-Voltage Variation in Sensor Node

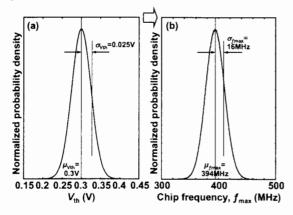

Since a frequency of 1.2 GHz and threshold voltage of 0.15 V in the Intel microprocessor are too fast and leaky for a node chip, we modify the design parameter. n in the Intel microprocessor is also small due to micro pipelining, however, we can mitigate it, and n is increased to three times in the node chip. As for the threshold voltage of the node chip,  $\mu_{\text{Vth}}$  is shifted to 0.3 V as shown in Fig. (a) in order to suppress a subthreshold-leakage current.  $V_{\text{dd}}$  is set to 1.2 V.

Fig. 3. Estimated distributions of threshold voltage and maximum operating frequency in sensor node.

We assume that the node chip is made with the same manufacturing process as the Intel microprocessor, and thus  $\sigma_{Vth}$  in the node chip is set to 0.025 V. Fig. (b) illustrates the estimated distribution of the maximum operating frequency under the conditions, where  $\mu$ =394 MHz and  $\sigma_{fmax}$ =16 MHz. Table 1 summaries the design parameters.

TABLE I. Design parameter comparison between Intel high-performance processor and node chip.

|              | Path length | Vdd   | μVth   | σVth    | μfmax   | σfmax    |

|--------------|-------------|-------|--------|---------|---------|----------|

| Intel µP [7] | 14 gates    | 0.9 V | 0.15 V | 0.025 V | 1.2 GHz | 0.06 GHz |

| Node chip    | 42 gates    | 1.2 V | 0.3 V  | 0.025 V | 394 MHz | 16 MHz   |

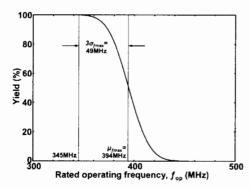

# 3) Yield of Node Chip

Although there is the variation of the maximum operating frequency in the node chips, a rated operating frequency is uniquely settled to all nodes, which is generally set lower to enhance yield. Fig. 4 is the yield curve of the node chips. If the margin is set to  $3\sigma_{\rm fmax}$ , in other words, if the rated operating frequency is 0.345 GHz (= $\mu_{\rm fmax}$ -3 $\sigma_{\rm fmax}$ ), the yield achieves 99.87%, which is high enough.

Fig. 4. Yield of node chips.

#### IV. POWER VARIATION

#### A. Power Variation in Microprocessor

Power optimization by controlling  $V_{\rm th}$  and  $V_{\rm dd}$  is a difficult problem. If  $V_{\rm th}$  is large,  $V_{\rm dd}$  must be large to maintain a speed of a circuit, which turns out to large power. To the contrary, if  $V_{\rm th}$  is small,  $V_{\rm dd}$  can be small, and thus a dynamic power can be small. However, this increases a subthreshold-leakage power. According to [10], a power consumed in a digital circuit is minimized when a subthreshold-leakage power occupies 30% of a total power at a threshold voltage of  $\mu_{\rm Vth}$ -3 $\sigma_{\rm Vth}$ .

Once a rated operating frequency is fixed,  $P_{\rm dyn}$  in (3) is fixed as well in all node chips.

$$P_{\rm dyn} = K_{\rm p} V_{\rm dd}^2 \,, \tag{7}$$

where  $K_p = K_2 f_{\rm op} C_{\rm L}$ . In the optimum design,  $P_{\rm leak}$  should be  $3P_{\rm dyn}/7$  when  $V_{\rm th} = \mu_{\rm Vth} - 3\sigma_{\rm Vth}$  according to [10]. Therefore, (4) is rewritten as follows:

$$P_{\text{leak}} = \frac{3}{7} K_{\text{p}} 10^{-\frac{V_{\text{th}} - (\mu_{\text{vth}} - 3\sigma_{\text{vth}})}{S}} V_{\text{dd}}^2,$$

(8)

which indicates that  $P_{\rm leak}$  is varied node-by-node.  $P_{\rm leak}$  is exponentially changed by the threshold-voltage variation.

### B. Power Variation in RF Part

When  $V_{\rm gs} = V_{\rm OD} + \mu_{\rm Vth}$  ( $V_{\rm OD}$  is called an overdrive voltage), (5) is rewritten as follows:

$$P_{RF} = \beta (V_{OD} + \mu_{Vth} - V_{th})^{2}$$

$$= \beta (V_{OD}^{2} + 2V_{OD}(\mu_{Vth} - V_{th}) + (\mu_{Vth} - V_{th})^{2})$$

$$= \beta (V_{OD}^{2} + 2V_{OD}(\mu_{Vth} - V_{th}))$$

$$(\because V_{OD} >> \mu_{Vth} - V_{th})$$

(9)

which exhibits that  $P_{\rm RF}$  is linearly changed by the threshold-voltage variation.

# C. Power Variation in Node Chip

Since the microprocessor and RF part are located on a same chip, the threshold-voltage variation commonly affects to both.

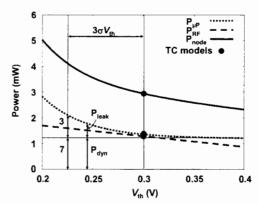

$P_{\mu P}$  is a sum of (7) and (8). Supposing that  $P_{\rm dyn}=1.2$  mW,  $K_{\rm p}$  becomes 1/1200 in (7) since  $V_{\rm dd}$  is 1.2 V in the design. The value of 1.2 mW is reasonable compared with [11]. In the conventional TC model without the threshold-voltage variation,  $V_{\rm th}$  only takes 0.3 V, and then  $P_{\mu P}$  would be set to  $P_{\rm dyn}+P_{\rm leak}=1.2+0.16=1.36$  mW. On the other hand in the proposed TV model,  $P_{\mu P}$  is distributed due to the variation of the subthreshold-leakage power as shown in Fig. 5.

Fig. 5. Power variations in node chip.

As for  $P_{RF}$ , we carried out a circuit-level simulation to evaluate the threshold-voltage variation in the RF part, assuming the LNA. The

$P_{\rm RF}$  variation exhibits the linear characteristics, and given as follows:

$$P_{\rm RF} = 10^{-3} K_4 (-3.43 V_{\rm th} + 2.10) V_{\rm DD} \tag{10}$$

where  $K_4$  is a fitting parameter.  $K_4$ =1 means that  $P_{\rm RF}$  is equal to  $P_{\rm dyn}$  of the microprocessor at a threshold voltage of 0.3 V, and  $P_{\rm RF}$  in this case is shown in the figure. In the conventional TC model,  $P_{\rm RF}$  would be fixed to 1.29 mW.

$P_{\rm node}$  in the conventional TC model eventually becomes  $(P_{\mu P} + P_{\rm RF})/K_{\rm DCDC} = (1.36 + 1.29)/0.9 = 2.943 mW. In the proposed TV model, an average power of the node chips, <math>\mu_{\rm Pnode}$ , is 2.976 mW, which is larger than the conventional one just by 1.12%.

### V. VERIFICATION WITH NETWORK SIMULATOR

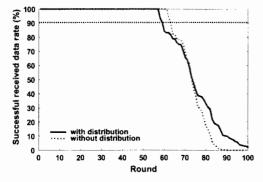

In this section, we introduce both power models with and without power variation in a network simulator, and investigate an impact of power variation on system-level performance from viewpoint of life time. The network simulator which we used is QualNet [2]. In the field of 100 x 100m<sup>2</sup>, 256 sensor nodes are deployed at random, and a base station is placed in the center. Application is data gathering where each sensor node transfers its sensed data into the base station every round which is set to 1,000 seconds. A physical layer protocol is Low Power Listening [12], and its duty cycle ratio is set to 0.5%. MAC layer protocol is PAMAS [13]. A network layer protocol is tiny diffusion [14], and an interest is flooded only once at the beginning of a simulation trial. Before defining a metric of network life time, we define data acquisition rate by the ratio of the amount of data received by the base station in a round to the amount of data generated by all nodes in the round regardless of their life-and-death. We define life time as duration in which successful data received rate is 90% or more. Fig. 6 shows characteristics of successful data received rate in the cases of TV and TC power model. The powers of a microprocessor and RF part are in the ratios 1:1. Recall that TV power model consumes slightly more power than TC power model by 1.121% on average in Fig. 6. We observe that TV power model leads to shorter life time than TC power model by 10.75% rather than 1.121%. In TV power model case, some nodes have inefficient power performance. This fact can make the network vulnerable. By contrast, this effect is not involved in TC power model. This is reason why the figure shows that TC power model indicates optimistic results compared with TV power model. Microprocessor power is distributed more than RF part power as previously mentioned in Section IV. Node power is eventually distributed more as microprocessor power becomes dominant. This leads to the situation where more nodes have inefficient power performance, which makes the network more vulnerable. If sensor nodes are more sophisticated in the future, the variation of microprocessor power will influence system-level performance.

Fig. 6. Data received rate, μP:RF=I:1

## VI. SUMMARY

In this paper, we developed the power consumption model, which we named TV power model, considering manufacture variation of subthreshold voltage in a processor and an RF circuit, and implement the model to QualNet. Simulation results showed that the conventional power model which we call TC power model optimistically estimates network life time longer than our proposed TV power model by 10.75% although TV power model consumes slightly more power than TC power model by 1.121%.

In our future research, we will consider not only systematic variation but also random variation and peripherals and power source variations. We suppose that these factors enlarge variation of node power performance, which has a more significant impact on system-level performance such as network life time.

# ACKNOWLEDGMENT

We would like to appreciate Mr. Shunsuke Baba with Oki Electric Industry Co., Ltd. for providing process parameters and technology files.

#### REFERENCES

- [1] NS2: see http://www.isi.edu/nsnam/ns

- [2] QualNet: see http://www.scalable-networks.com, Scalable network technology.

- [3] A. P. Chandrakasan, R. Min, M. Bhardwaj, S. Cho, and A. Wang, "Power-Aware Wireless Microsensor Systems", IEEE Signal Processing Magazine, March 2002

- [4] P.Hazucha, S.T.Moon, G.Schrom, F.Paillet, D.S.Gardner, S.Rajapandian, T.Karnik, "A linear RRRregulator with Fast Digital Control for Biasing Integrated DC-DC Converters," IEEE international Solid-State Circuits Conference, No. 29.2, 2006.

- [5] T. Sakurai, A. R. Newton, "Alpha-Power Law MOSFET Model and its Applications to CMOS Inverter Delay and Other Formulas," IEEE Journal of Solid-State Circuits, vol.25, No.2, April 1990

- [6] H. Kawaguchi, K. Kanda, K. Nose, S. Hattori, D. D. Antono, D. Yamada, T. Miyazaki, K. Inagaki, T. Hiramoto, and T. Sakurai,"A 0.5-V, and 400-MHz, VDD-Hopping Processor with Zero-VTH FD-SOI Technology," IEEE International Solid-State Circuits Conference Digest of Technical Papers, No. 6.3, pp. 106-107, Feb. 2003.

- [7] T. Sakurai, H. Kawaguchi, and T. Kuroda, "Low-power CMOS design through VTH control and low-swing circuits (invited)," Proceeding of IEEE International Symposium on Low Power Electronics and Design, pp. 1-6, Aug. 1997.

- [8] B. Razavi, "Design of Analog CMOS Integrated Circuits," published by "McGraw-Hill Publishing Co.," 1st Oct. 2003, ISBN: 0072372710

- [9] J. W. Tschanz, J. T. Kao, S. G. Narendra, R. Nair, D. A. Antoniadis, and A. P. Chandrakasan, "Adaptive Body Bias for reducing impacts of die-to-die and within-die parameter variations on microprocessor frequency and leakage," IEEE Journal of Solid-State Circuits, vol. 37, no. 11, Nov. 2002.

- [10] K.Nose, and T. Sakurai and "Optimization of VDD and VTH for Low-Power and High-SpeedApplications" ASPDAC, pp.469-474, Jan. 2000.

- [11] M.Izumikawa, Member, IEEE, H. Igura, Associate member, IEEE, K.Furuta, H.Ito,H.Wakabayashi, K.Nakajima, T.Mogami, T.Horiuchi, and M.Yamashita, Member, IEEE, "A 0.25-µm CMOS 0.9-V 100-MHz DSP Core," IEEE Journal of Solid-State Circuits, vol. 32, No. 1, January 1997.

- [12] J. Hill and D. Culler, "Mica: a wireless platform for deeply embedded networks, "IEEE Micro, Vol.22, pp.12-24, and 2002. [low power listening]

- [13] S. Singh and C.S.Raghavendra and "PAMAS:Power aware multi-access protocol with signalling for ad hoc networks," ACM SIGCOMM Computer communication Review, pp.5-26, 1998.

- [14] E.Osterweil, and D.Estrin, "Tiny Diffusion in the Extensible Sensing System at the James Reserve," May 2003, see http://www.cens.ucla.edu/~eoster/tinydiff