# 1.27-Gbps/pin, 3mW/pin Wireless Superconnect (WSC) Interface Scheme

Kouichi Kanda, Danardono Dwi Antono, Koichi Ishida, Hiroshi Kawaguchi, Tadahiro Kuroda\*,and Takayasu Sakurai

# University of Tokyo \* Keio University Japan

# Outline

- Background

- **WSC** scheme overview

- Circuit design

- Measurement

- Simulation

- Conclusion

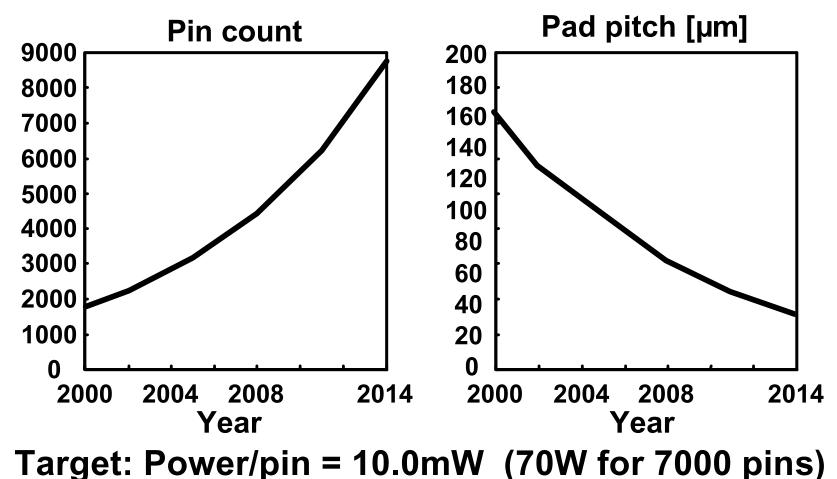

## Trend in assembly predicted by ITRS

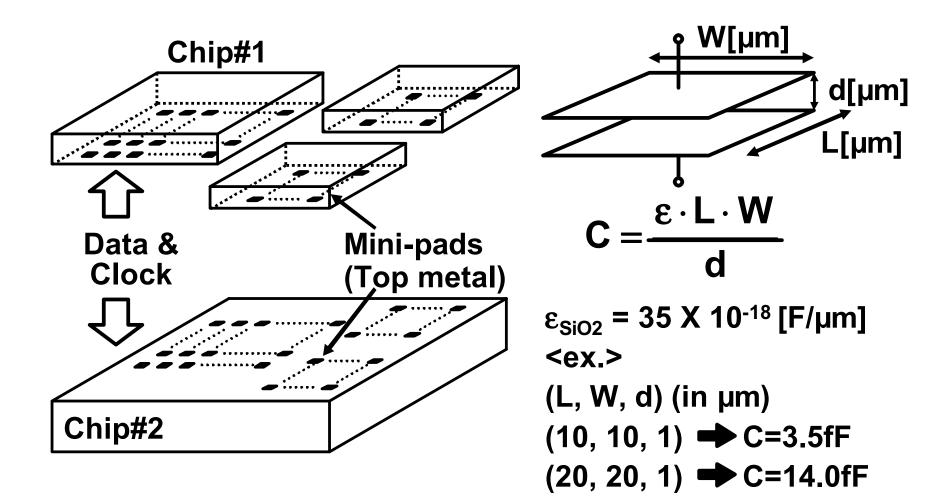

Pad pitch =  $20\mu m$  (7000 pads in 2.8mm<sup>2</sup>)

#### Wireless superconnect scheme overview

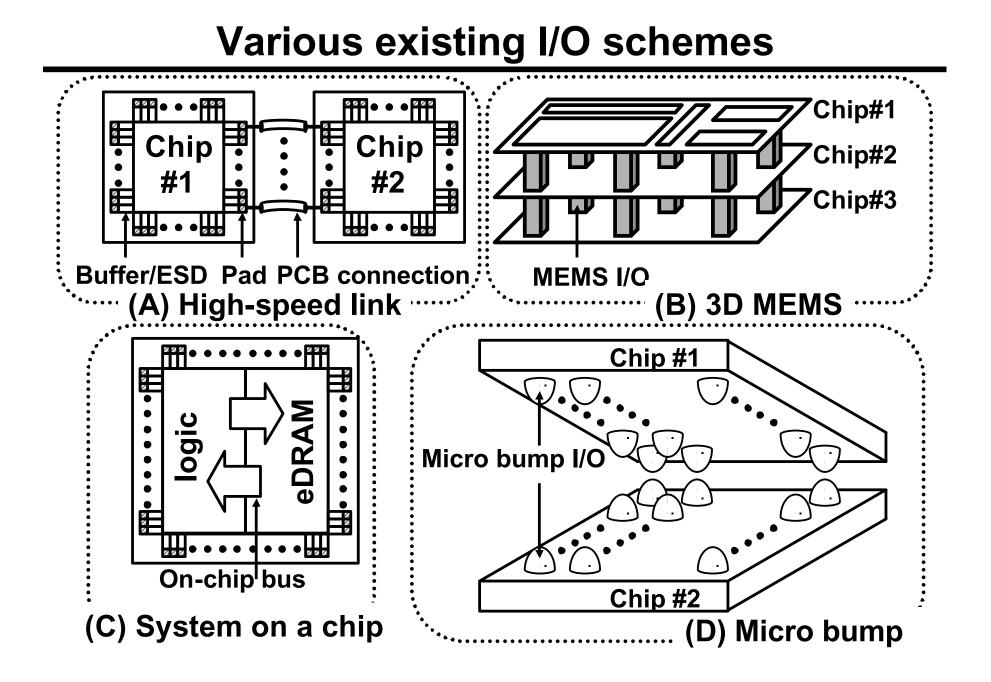

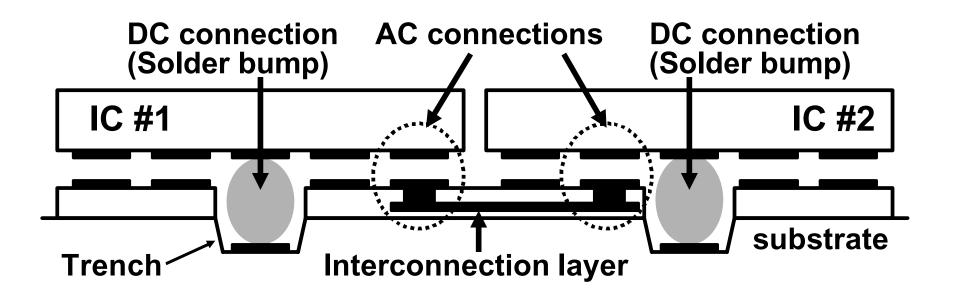

S. Mick et al. "4Gbps High-Density AC Coupled Interconnection," Custom Integrated Circuits Conf., 2002, pp.133-140. (North Carolina State University)

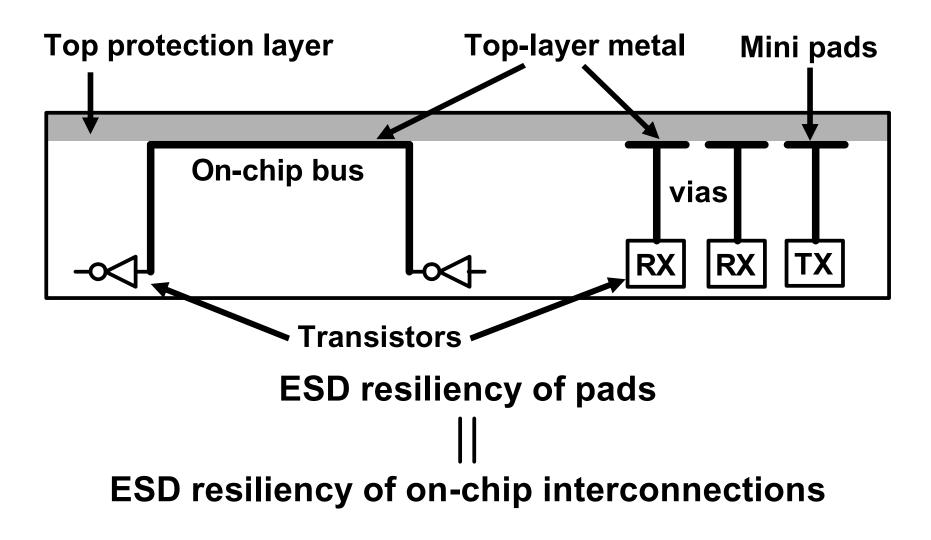

## **ESD in WSC**

### **Comparison of interface schemes**

|           | Serial<br>link | 3D<br>MEMS | SOC | μ<br>bump | WSC                                   |  |

|-----------|----------------|------------|-----|-----------|---------------------------------------|--|

| Bandwidth |                | +          | ++  | +         | •                                     |  |

| Cost      | +              |            | -   | +         | ╋╋                                    |  |

| Area      |                | ++         | -   | +         | •                                     |  |

| ESD       |                | -          | -   | -         | • <b>•</b> •                          |  |

| Power     | -              | +          | ++  | +         | <b>-</b>                              |  |

| TAT       | -              |            |     | +         | ╋╋                                    |  |

|           |                |            |     |           | · · · · · · · · · · · · · · · · · · · |  |

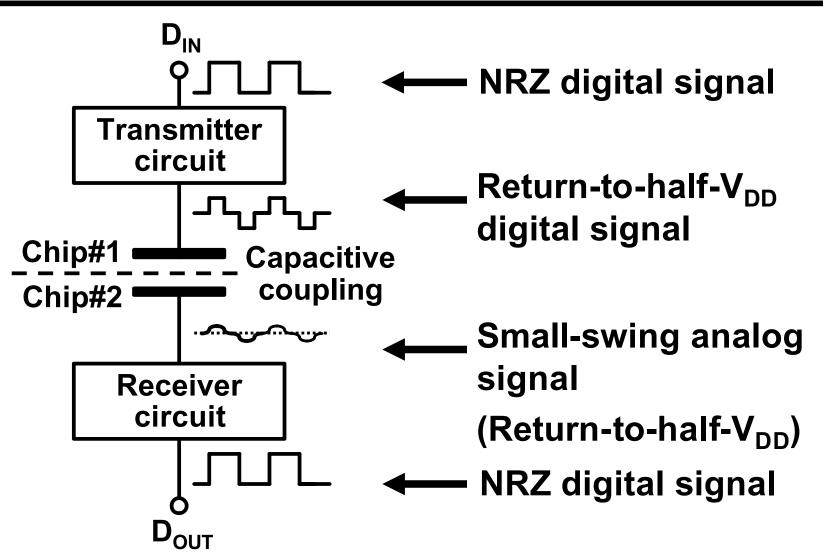

# Signaling method in WSC

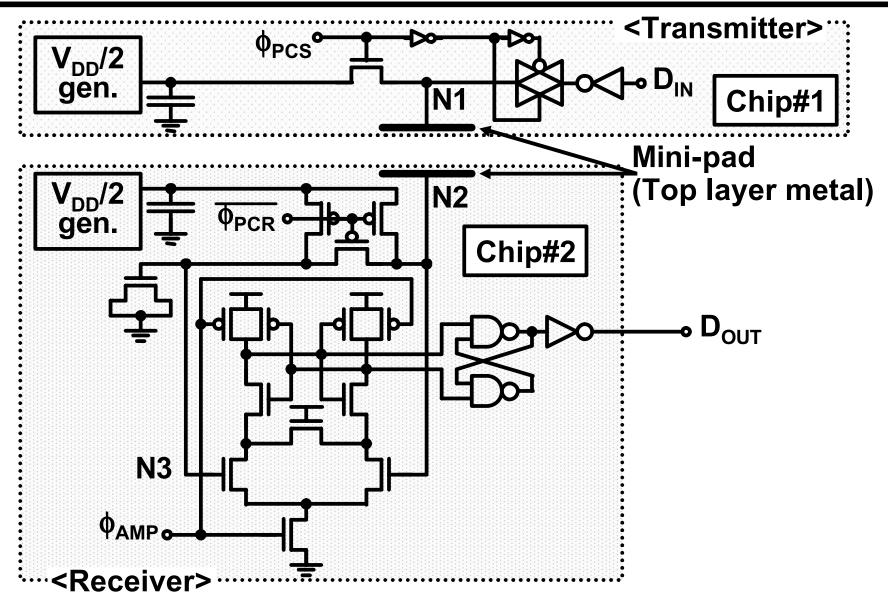

### **Circuit diagram of transmitter and receiver**

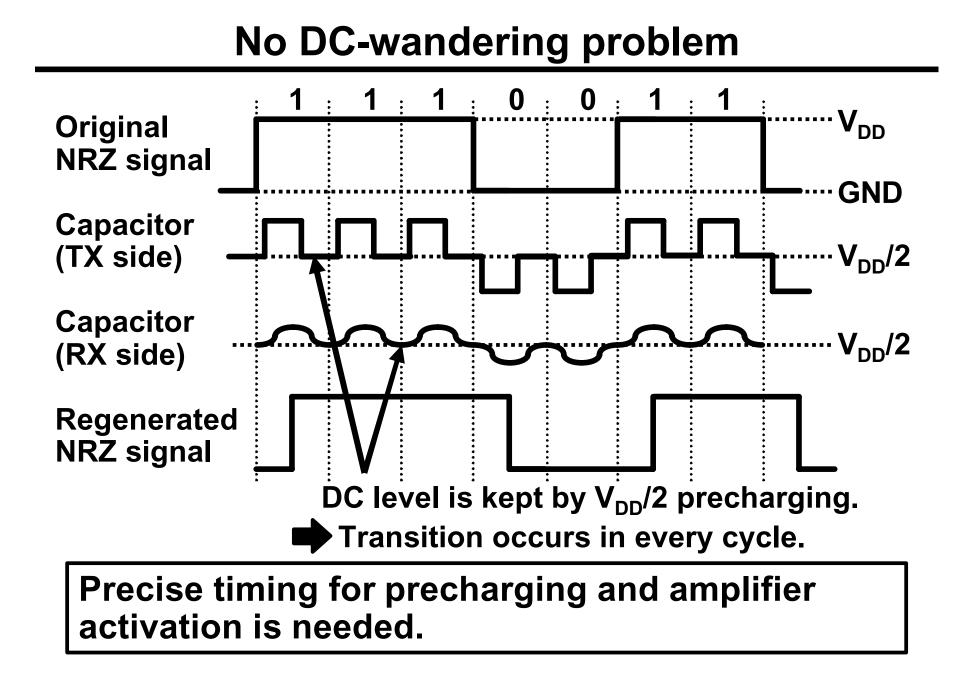

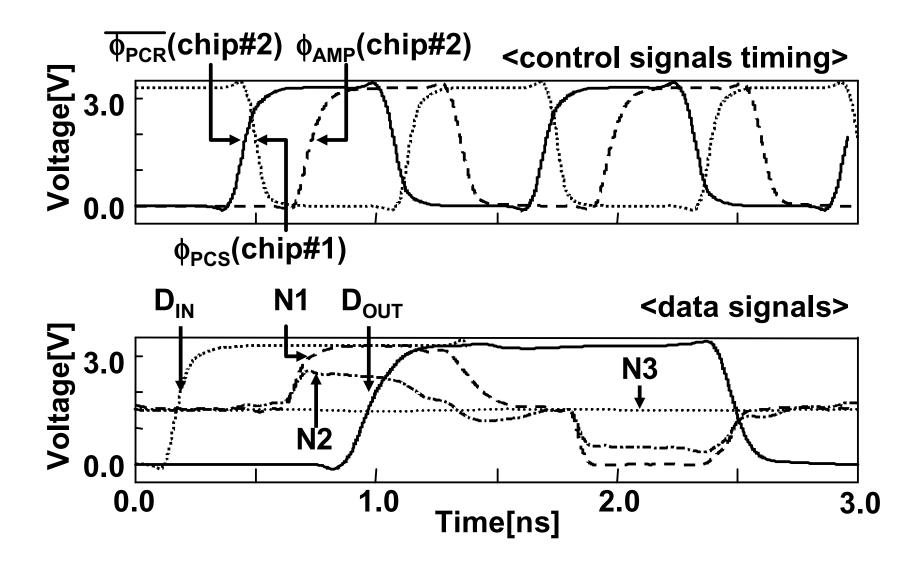

### **Operating waveform**

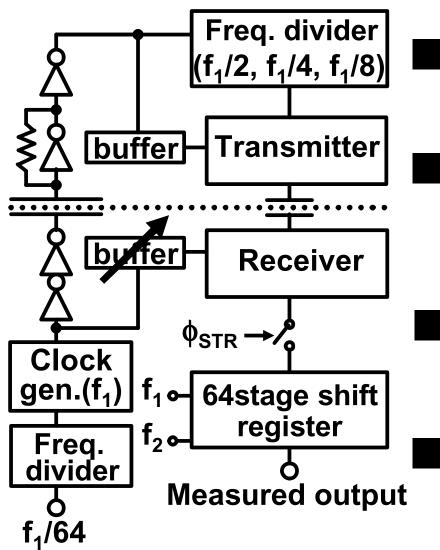

# **Test environment**

On-die clock generation for high frequency

Receiver timing control with a variable delay buffer

Monitoring clock frequency with a divider

Storing data sequences in a shift register

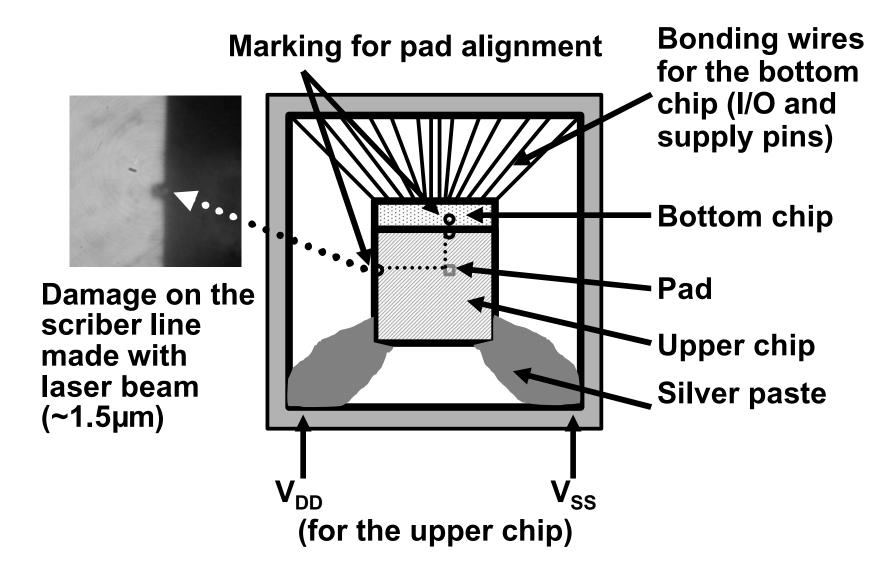

#### **Measurement setup**

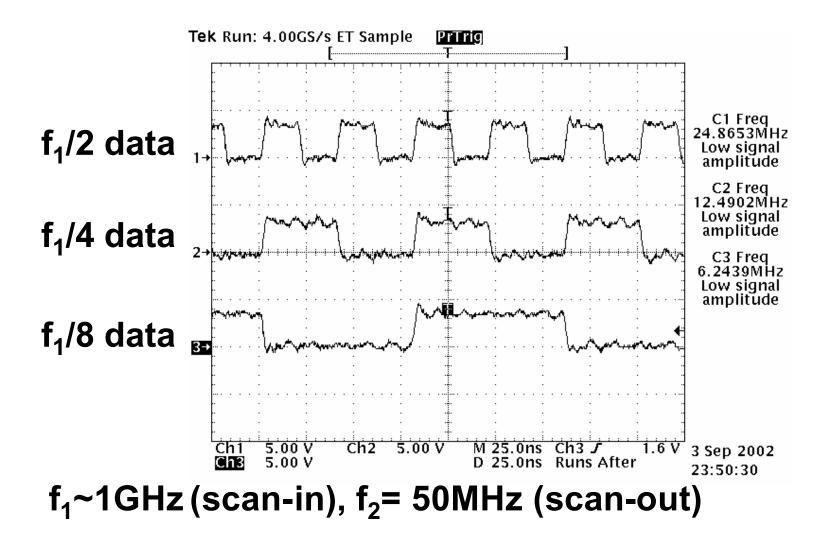

#### **Measured waveform**

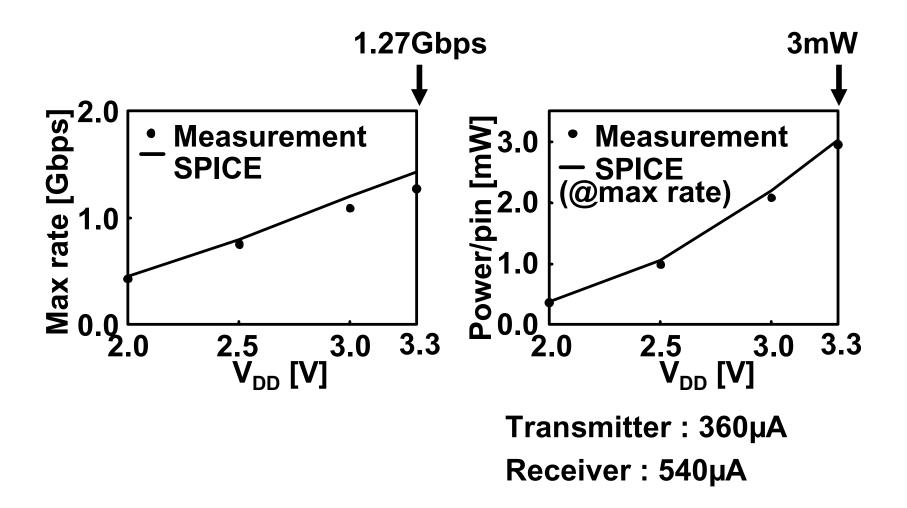

#### Measured and simulated WSC performance

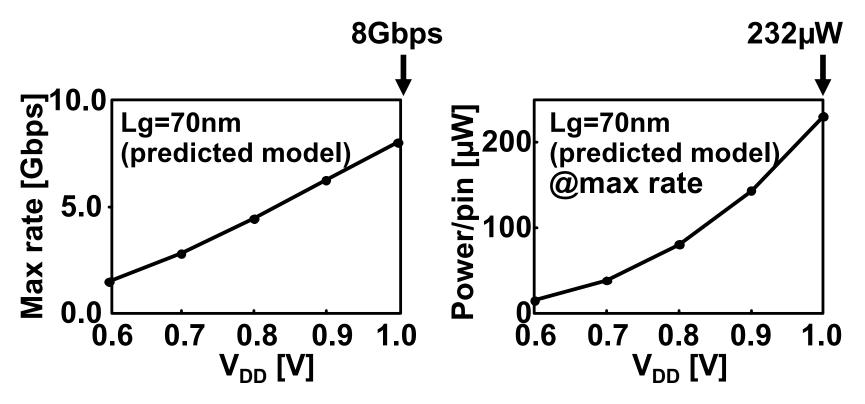

#### Simulated WSC performance in 70nm tech.

Future 7000 I/O pads can operate at 8GHz with only 1.63W.

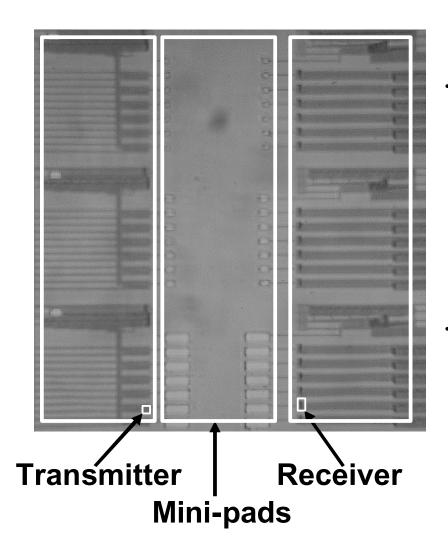

## Test chip microphotograph

#### Technology

0.35µm CMOS Triple metal 3.3V supply

I/O design

Transmitter:20µmX20µm Receiver: 12µmX12µm Pad: 10µmX20µm

- WSC interface is proposed for high-density and low-power chip-to-chip communications.

- Low I/O capacitive load is achieved by small pad size and elimination of ESD structure.

- 1.27-Gbps with 3mW from 3.3V power supply was measured in 0.35µm CMOS technology.

- Simulation results in 70nm technology show possibility of 7000 I/O pads operating at 8-Gbps with 1.63W in 2.82mm<sup>2</sup>.

Mr. Hiroyuki Hara and Mr. Tetsuya Fujita at Toshiba Corporation for experiments support

Dr. Tohru Ishihara and Dr. Makoto Ikeda at VDEC, University of Tokyo for chip fabrication support

(VDEC = VLSI Design and Education Center)