### Zigzag Super Cut-off CMOS (ZSCCMOS) Block Activation with Self-Adaptive Voltage Level Controller

An Alternative to Clock-Gating Scheme in Leakage Dominant Era

> <sup>1,2</sup>Kyeong-Sik Min, <sup>1</sup>Hiroshi Kawaguchi, and <sup>1</sup>Takayasu Sakurai

<sup>1</sup>University of Tokyo, Tokyo, Japan <sup>2</sup>Kookmin University, Seoul, Korea

# Outline

- Introduction

- Zigzag Super Cut-off CMOS (ZSCCMOS)

- ZSCCMOS Block Activation

- Control Circuitry with Adaptive Voltage Level Detector

- Measurement & Discussion

- Summary

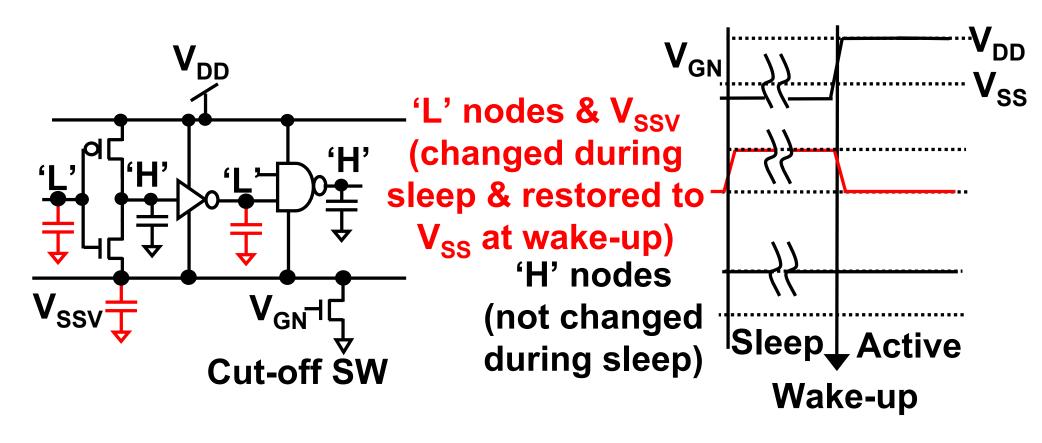

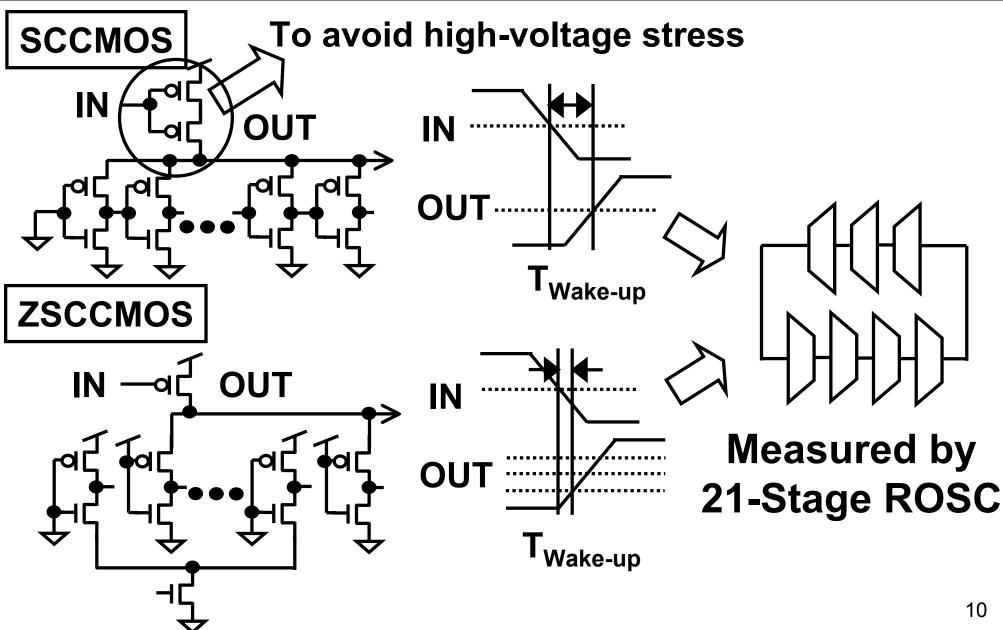

## Previous Leakage Suppression Scheme: Super Cut-off CMOS (SCCMOS)

Full swing of 'L' nodes and V<sub>SSV</sub> nodes at wake-up

Long wake-up time and high rush current at wake-up

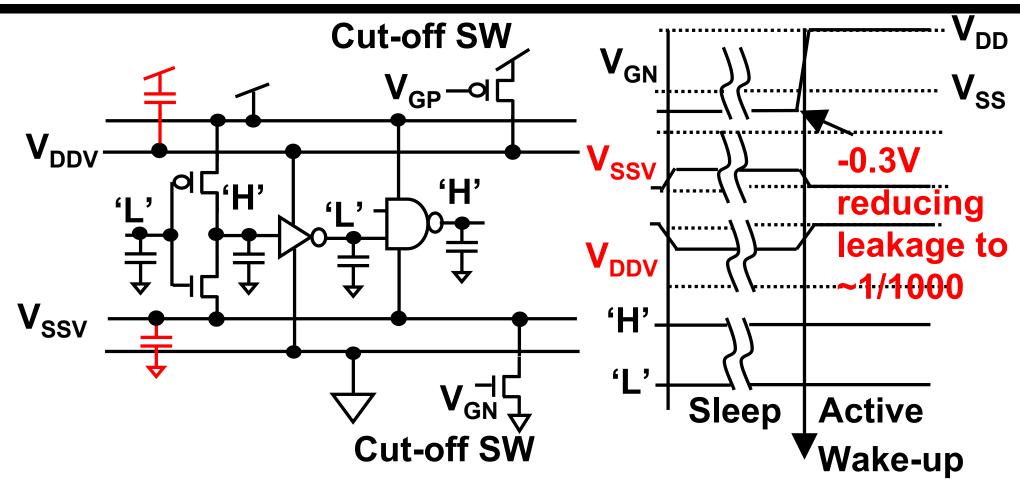

# Zigzag Super Cut-off CMOS (ZSCCMOS)

Small voltage change of V<sub>SSV</sub> and V<sub>DDV</sub> due to reversesource biasing effect

No voltage change of 'H' and 'L' nodes at wake-up

=> Short wake-up time and low rush current at wake-up <sup>4</sup>

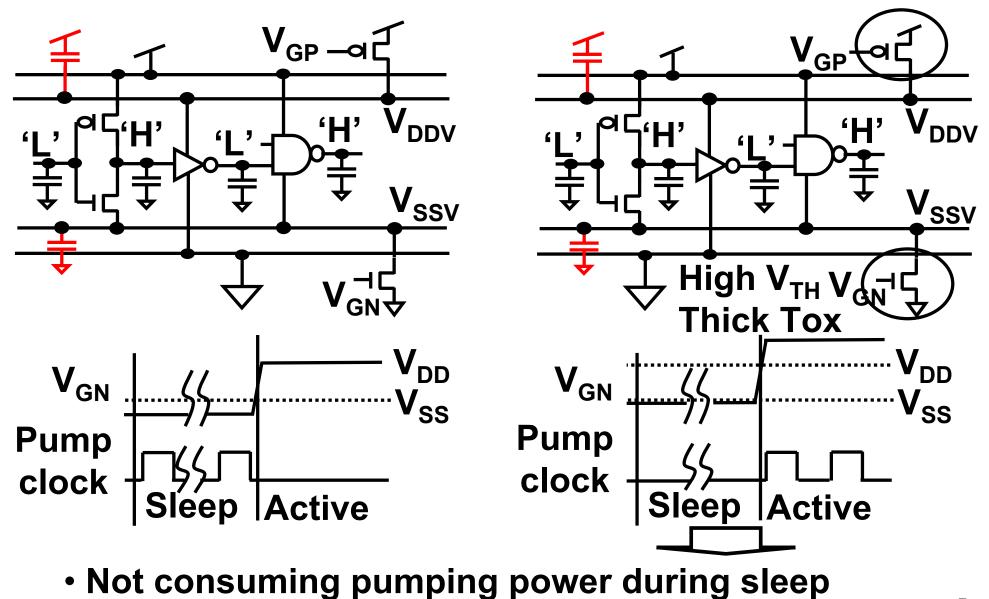

# **Derivative of ZSCCMOS (ZBGMOS)**

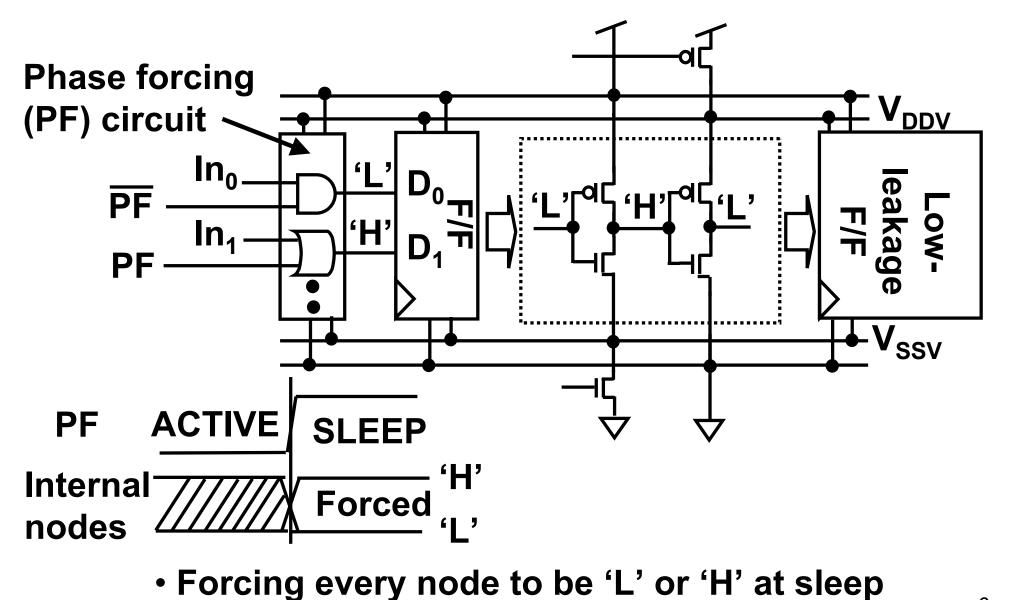

### ZSCCMOS Block Activation Scheme with Phase Forcing

© 2003 IEEE International Solid-State Circuits Conference © 2003 IEEE

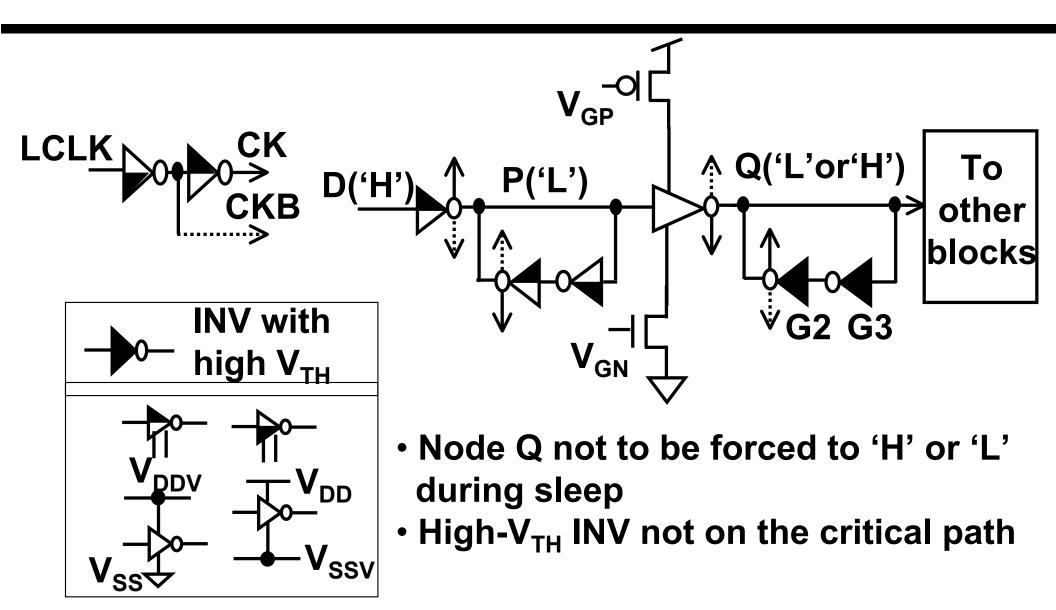

#### Low-Leakage Flip-Flop

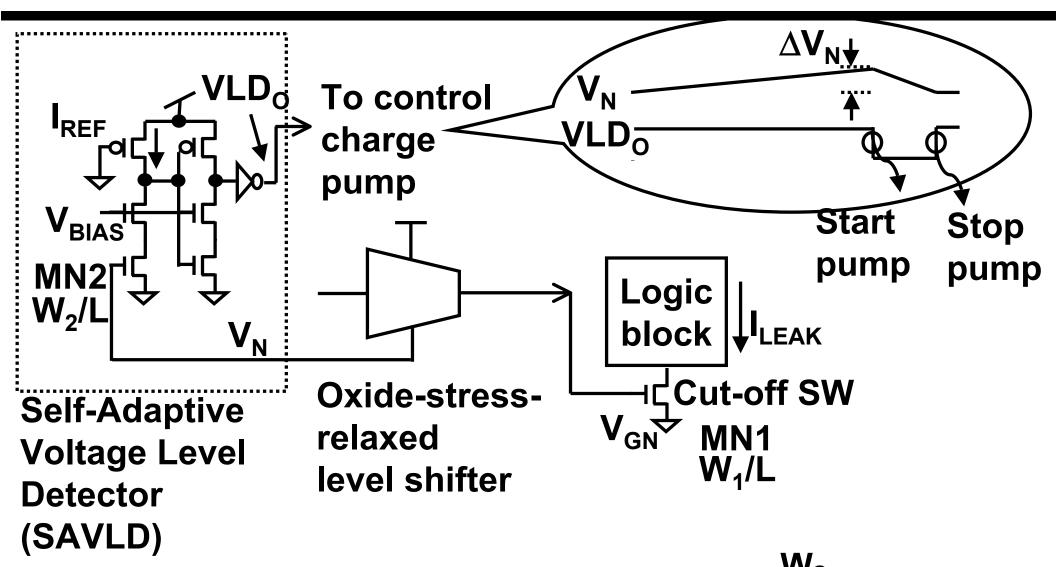

## **Control Circuit for NMOS Cut-off Switch**

• Self-adaptively adjusting  $V_N$  as  $I_{LEAK} \frac{V_2}{W_A} = I_{REF}$

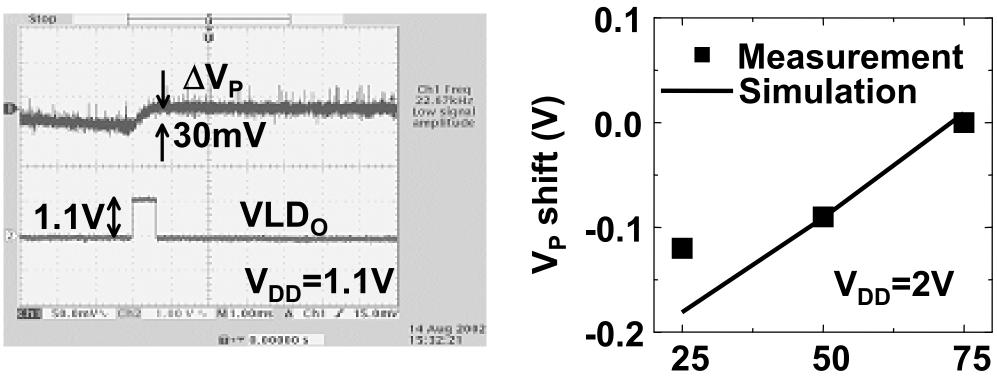

# Measurement of Self-Adaptive V<sub>P</sub> Level Detector

**Temperature (°C)**

- Fabricated in 0.6-µm CMOS N-well process

- Self-adaptive V<sub>P</sub> adjusting with varying temperature

#### **Measurement Set-up**

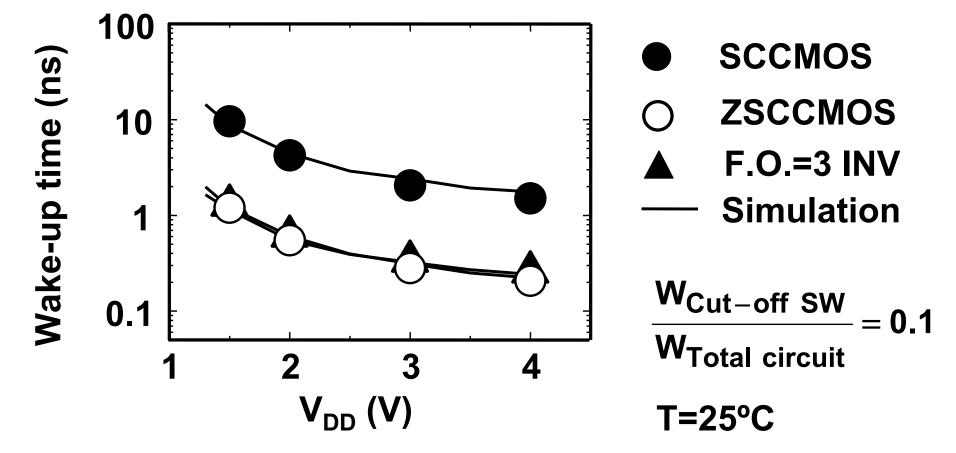

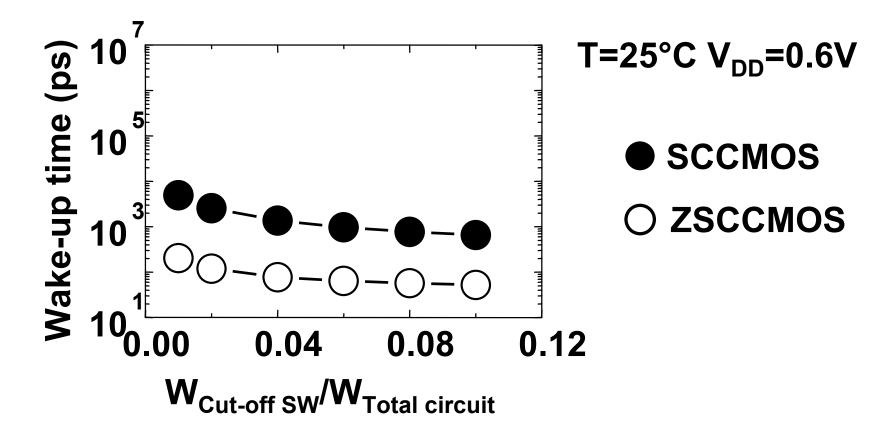

#### **Comparison of Measured Wake-up Time**

- Fabricated in 0.6-µm technology

- 8 times shorter wake-up time of ZSCCMOS than SCCMOS

#### **Comparison of Simulated Wake-up Time**

- Simulation by assuming 70-nm technology using Berkeley Predictive MOSFET Technology Model (BPTM)

- 12 times shorter wake-up time of ZSCCMOS than SCCMOS

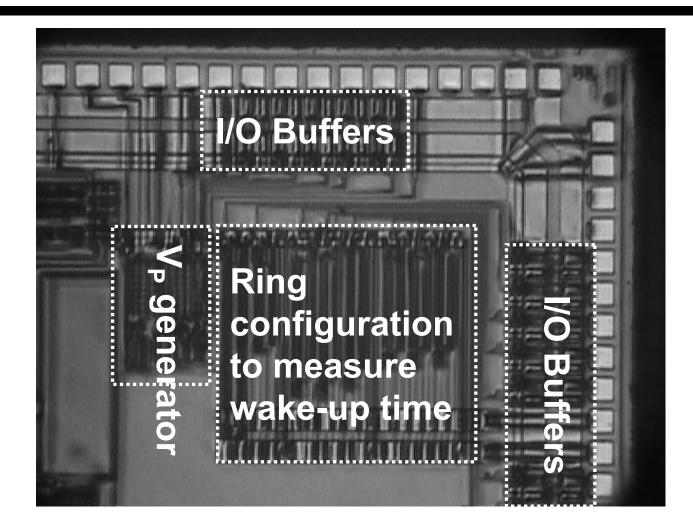

### **Test Chip Micrograph**

Fabricated in 0.6-µm CMOS technology

# Summary

- Zigzag scheme presented for leakage dominant era

- ZSCCMOS: ~200-ps wake-up time and smaller rush current than SCCMOS

- ZSCCMOS block activation scheme reduces leakage power to ~1/1000 when inactive.

- Gate voltage of cut-off SW self-adjusted so as to set I<sub>LEAK</sub> constant over PVT variation