PAPER Special Section on Analog Circuits and Related SoC Integration Technologies

# An I/O-Sized ADC with Second-Order TDC and MOM Capacitor Voltage-to-Time Converter\*

Keisuke OKUNO<sup>†a)</sup>, Student Member, Toshihiro KONISHI<sup>†</sup>, Nonmember, Shintaro IZUMI<sup>†</sup>, Masahiko YOSHIMOTO<sup>†</sup>, and Hiroshi KAWAGUCHI<sup>†</sup>, Members

**SUMMARY** We present an I/O-size second-order analog to digital converter (ADC) combined with a time-to-digital converter (TDC) and a voltage-to-time converter (VTC). Our proposed VTC is optimized for metal-oxide-metal (MOM) capacitances, and is charged to the MOM capacitances by an input voltage. In a standard 65-nm CMOS process, a signal to noise and distortion ratio (SNDR) of 50 dB (8 bits) is achievable at an input signal frequency of 78 kHz and a sampling rate of 20 MHz, where the respective area and power are 6468 mm<sup>2</sup> and 509  $\mu$ W. The measured maximum integral nonlinearity (INL) of the proposed ADC is -1.41 LSBs. The active area of the proposed ADC is smaller than an I/O buffer. The proposed ADC is useful as an ADC I/O.

key words: ADC, I/O-size, VTC, MOM capacitance

#### 1. Introduction

Various techniques have been developed to realize ubiquitous computing for sensors. With implementation of more sensors, more analog-to-digital converters (ADCs) are required by the many sensors to digitize the many channel signals [1], [2]. To date, the ADCs on an LSI chip have been limited numerically by the chip area. To achieve high accuracy, for instance, an SAR ADC requires large capacitors for which the area cannot be scaled down with process scaling.

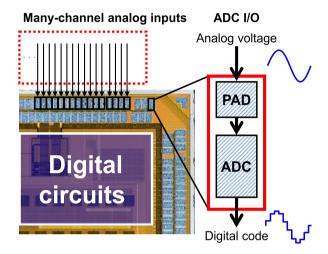

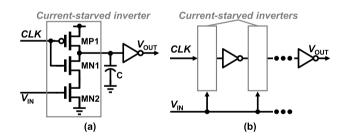

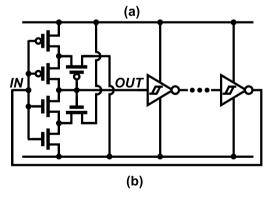

Figure 1 presents the points of emphasis of this work. We propose a smaller ADC than an I/O buffer size. We adopt a time-to-digital converter (TDC) suited to multiple-channel applications because it can be configured by digital circuits and because it can be extended easily to advanced CMOS process node. However, the small-area TDC, which can be realized within performance constraints at a low cost, needs an external circuit to convert an analog signal to a time-domain signal. Several voltage-to-time converters (VTCs) have been reported, one of which is a combination of a current-starved inverter and a capacitor [3]–[5] in Fig. 2(a). Another VTC uses a voltage-to-delay line comprised of the current-starved inverters [6]–[8] in Fig. 2(b). The current-starved inverter controls its output pulse width based on an analog input voltage ( $V_{\rm IN}$ ) applied to MN2, and

Manuscript received October 14, 2014.

Manuscript revised February 2, 2015.

a) E-mail: okuno@cs28.cs.kobe-u.ac.jp DOI: 10.1587/transele.E98.C.489

Fig. 1 ADC I/Os for multiple-channel analog inputs.

Fig. 2 Conventional VTC circuits.

thus can be implemented in a small area; its linearity is, however, strongly affected by the gate-source voltage. The high-linearity range is narrow, which results in a small input voltage range.

To achieve a small area yet a large input voltage range, we propose a new VTC using metal—oxide—metal (MOM) capacitances in the next section. Our proposed VTC achieves a large input voltage range by charging the MOM capacitance and detecting its discharging time. Although the MOM capacitances require a certain area on higher metals, ADC circuitry can be accommodated under the MOM capacitances; thus, an area overhead is minimized. We explain an I/O-sized ADC architecture with the proposed VTC in Section 3. Measured results with a test chip are described in Section 4. In Section 5, we discuss the nonlinearity in the proposed ADC. The final section summarizes this paper.

<sup>&</sup>lt;sup>†</sup>The authors are with the Department of Computer Science and Systems Engineering, Kobe University, Kobe, 657-8501, Japan.

<sup>\*</sup>This is the extended version of the published paper at IEEE ICECS 2014 [19].

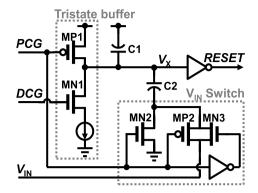

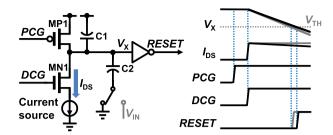

Fig. 3 Schematic of the proposed voltage-to-time converter.

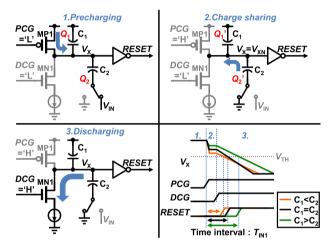

Fig. 4 Operation of the proposed VTC core circuit.

#### 2. Proposed Voltage-to-time Converter Core Circuit

A schematic of our proposed VTC core is depicted in Fig. 3. Our proposed VTC circuit, which consists of two MOM capacitances, converts  $V_{\rm IN}$  to a time interval. The circuit changes a discharging charge by  $V_{\rm IN}$ . The two MOM capacitances,  $C_1$  and  $C_2$ , are connected with the supply voltage (VDD) and a  $V_{\rm IN}$  switch circuit. The  $V_{\rm IN}$  switch circuit propagates a  $V_{\rm IN}$  analog voltage or the ground (VSS) to  $C_2$ . Therefore the charge amount of  $C_2$  is changed by  $V_{\rm IN}$ . A tristate buffer includes a current source. The non-overlap signals (DCG and PCG) control the  $C_1$  and  $C_2$  charges and discharges.

Figure 4 shows the mechanism and the timing diagram of proposed VTC core circuit. First, while DCG and PCG are 'low,' the pMOS transistor (MP1) charges  $V_X$  to VDD; the charge on  $V_X$  is a sum of the charges of  $C_1$  and  $C_2$  represented as

$$Q_1 + Q_2 = 0 + C_2 \cdot (VDD - V_{IN}), \tag{1}$$

where  $Q_1$  and  $Q_2$  are charges of  $C_1$  and  $C_2$ . Next, when the *PCG* becomes 'high,' the  $V_{\rm IN}$  switch is flipped from  $V_{\rm IN}$  to *VSS*. The charges of  $C_1$  and  $C_2$  are shared at  $V_{\rm X}$ . Therefore,

Fig. 5 Simulation result of the VTC core.

its voltage is controlled by  $V_{\rm IN}$  as

$$Q_1' + Q_2' = C_1 \cdot (V_{XN} - VDD) + C_2 \cdot (V_{XN} - VSS),$$

(2)

where  $V_{\rm XN}$  is a stable voltage after *PCG* becomes 'high.' Eventually, from (1) and (2),  $V_{\rm XN}$  can be given as

$$V_{\rm XN} = VDD - \frac{C_2}{C_1 + C_2} \cdot V_{\rm IN}.$$

(3)

The charge amount is defined by the capacitances of  $C_1$  and  $C_2$ , and the voltage of  $V_{\rm IN}$ . Next, DCG becomes 'high,' and the nMOS transistor (MN1) and a current source discharges the charge. When  $V_{\rm X}$  becomes lower than a threshold voltage ( $V_{\rm TH}$ ) of the inverter, RESET becomes 'high.' From (3), the interval in which  $V_{\rm X}$  becomes lower than  $V_{\rm TH}$  depends on  $V_{\rm XN}$  and depends on the time at which the rising edge of RESET is changed. Therefore, this VTC core circuit can convert the voltage domain to the time domain.

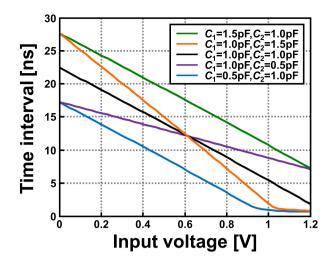

Figure 5 presents the SPICE simulation result of the proposed VTC core circuit. The vertical axis is the time interval from the rising edge of PCG to the rising edge of *RESET.* The horizontal axis is the analog input voltage  $V_{\rm IN}$ . In this simulation,  $V_{IN}$  is swept from 0 V to 1.2 V. As  $C_1$  and  $C_2$  become larger, the input voltage range and the conversion gain are enlarged, respectively; the larger capacitances, however, occupy a large area. Hence, there is a trade-off between the input voltage range, the conversion gain, and the area. To achieve a 1.0-V input voltage range and a 25-ns time interval (note that the time interval is limited to a half of a sampling period in our design, which is 25 ns.), we take  $C_1 = C_2 = 1$  pF. The output characteristic is not completely linear because the discharging speed of the current source is not perfectly constant. To eliminate the nonlinearity characteristics, the proposed ADC has a nonlinearity corrector (see the next section).

## 3. I/O-Sized ADC with Proposed VTC

We propose an IO-sized ADC that consists of the small area

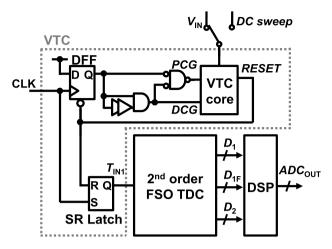

Fig. 6 Proposed I/O-sized ADC architecture.

FSO\*: Frequency shift oscillator QNP\*\*: Quantization noise propagator

Fig. 7 Schematics of (a) FSO TDC and (b) Schmitt trigger inverter ring.

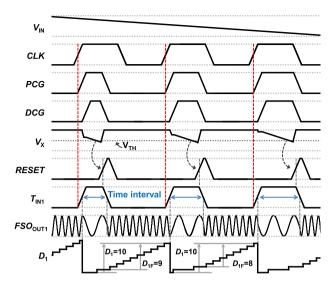

VTC and a frequency shift oscillator (FSO) TDC [9], as presented in Fig. 6. The VTC generates non-overlap signals, DCG and PCG, using a clock signal (CLK) to control the VTC core circuit. An SR Latch connected to the VTC core circuit outputs the time interval,  $T_{\rm INI}$  (time from the rising edge of CLK ( $\approx PCG$ ) to the rising edge of RESET), as explained in the previous section. The VTC core circuit is precharged again by its own RESET. In doing so, it is possible to make the circuit operation fast and to prepare for the next CLK pulse.

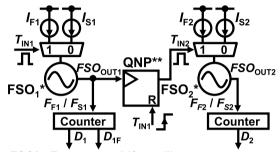

Figure 7(a) shows the architecture of the second-order  $\Delta\Sigma$  FSO TDC.  $T_{\rm IN1}$  is converted to digital values ( $D_1$  and  $D_{\rm 1F}$ ) by the first-stage FSO TDC (FSO<sub>1</sub>), which oscillates at a low frequency ( $F_{\rm F1}$ ) or high frequency ( $F_{\rm S1}$ ).

Fig. 8 Schematic of FSO and Schmitt trigger inverter ring.

The FSO TDC has a first-order noise shaping characteristic and achieves higher-order noise shaping by propagating its quantization noise to the next-stage FSO TDC: The quantization noise propagator (QNP) propagates the quantization noise to the next-stage FSO TDC. The QNP output  $(T_{\rm IN2})$  includes the previous quantization noise, which is digitized as a digital code  $(D_2)$  by the second-stage FSO TDC. The digital signal processor (DSP in Fig. 6) after the FSO TDCs calculates the final digital output  $(ADC_{\rm OUT})$  from  $D_1$ ,  $D_{\rm IF}$ , and  $D_2$  [9]. After converting an analog voltage to the digital code, the ADC can correct its nonlinearity using the DSP because the VTC characteristic is monotonic.

In the FSO TDC, the performance is affected by a timing jitter in the inverter of the oscillator, which determines its noise floor. To reduce the timing jitter, enlarging a transistor size in the oscillator is an effective way [10]; a circuit area and power are, however, increased. Instead, we adopt an FSO comprised of Schmitt trigger inverters, as illustrated in Fig. 7(b), which can absorb a power supply noise and reduce its jitter [11].

Figure 8 shows the operating waveforms of the proposed ADC. When CLK becomes 'high,' the DFF outputs 'high' for PCG and DCG. After DCG enables 'high,'  $V_X$  begins to be discharged toward VSS;  $V_X$  is, however, precharged on the way again by a trigger of RESET pulse when  $V_X$  crosses  $V_{TH}$ . Then,  $T_{IN1}$  becomes 'low.' That is, the SR latch generates the output pulse ( $T_{IN1}$ : time from the rising edge of CLK to the rising edge of RESET). The  $T_{IN1}$  width is defined by  $V_{IN}$ . After the VTC converts  $V_{IN}$  to  $T_{IN1}$ , the FSO TDC converts  $T_{IN1}$  to a digital code using a frequency difference.

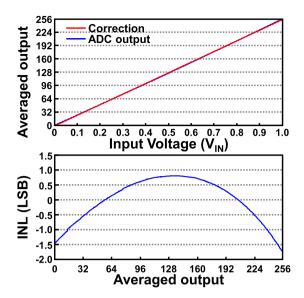

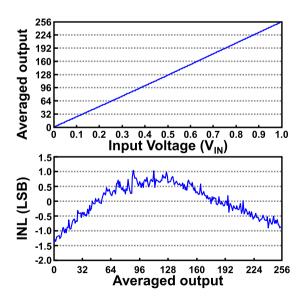

After converting to the digital code with the ADC, the DSP corrects the VTC nonlinearity and suppresses harmonic noises. To correct the ADC output, the DSP needs the voltage to digital characteristic. The ADC is applied a ramp signal at an initial calibration phase. Figure 9 shows the ADC characteristic of the SPICE simulation result. The

Fig. 9 Characteristics of the original ADC output and calculation.

blue line shows the averaged ADC output at a sampling rate of 20 MHz with 500 kHz low-pass filtering. The red line is an approximation straight line of the blue line. The integral non-linearity (INL) in the figure shows the deference of the blue and red line. The coefficients of the nonlinearity correction for the DSP are obtained by the DC sweep in Fig. 6 at the initial calibration phase. By correcting the ADC output with this method, the DSP cancels the harmonic noise.

#### 4. Measurement Results

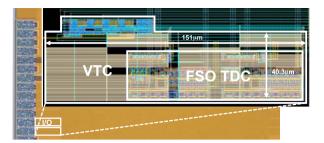

A test chip was made using a 65-nm CMOS process (Fig. 10). The VTC occupies  $6468 \, \mu \text{m}^2$  as an active area. The MOM capacitance consists of higher metal to put in the FSO TDC under the VTC. The MOM capacitance needs somehow large area; however the ADC needs no additional area without the VTC because the MOM capacitance consists of the higher metals. A digital input I/O in a 65 nm occupies  $6800 \, \mu \text{m}^2$ . The proposed ADC is 95.1% of the digital I/O, and is useful as an ADC I/O to convert a signal from analog to digital. The total power consumption is  $509 \, \mu \text{W}$ .

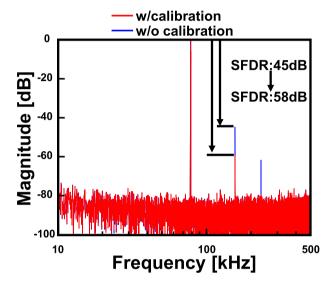

Figure 11 shows the measured output spectra of the proposed ADC. In the spectra, the input signal frequency is 78 kHz at a 20-MHz sampling rate. The original signal-to-noise and distortion ration (SNDR) in Fig. 11 is 43 dB at a bandwidth of 500 kHz and a spurious free dynamic range (SFDR) is 45 dB. The harmonics of ADC are produced by the nonlinearity of the VTC. After making the nonlinearity correction, the SFDR is improved to 58 dB, and the SNDR is improved to 50 dB, which exhibits an 8-bit resolution ADC.

Next the INL of the proposed ADC is measured by applying a ramp input. The input range is from 0.0 V to 1.0 V. The measured result of the DC transfer curve at a sampling rate of 20 MHz with 500 kHz low-pass filtering is shown in Fig. 12. The measured maximum INL is -1.41 LSBs.

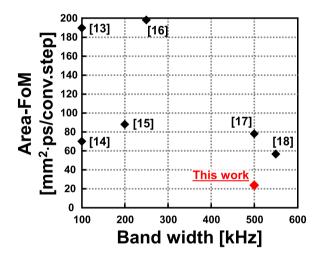

The test chip performance is summarized in Table 1 and Fig. 13. Our purpose is the area reduction of the ADC.

Fig. 10 Micrograph of the proposed ADC chip.

Fig. 11 Output spectra of IO-sized ADC w/o calibration and w/calibration.

Fig. 12 Measured static performance. (a) DC transfer, (b) INL.

Therefore, we compare area-FoMs of other state-of-the-art ADCs [12]. Our proposed ADC exhibits better area-FoM among the near-bandwidth ADCs.

| Table 1 | Chip Characteristics. |

|---------|-----------------------|

| Table I | Chip Characteristics. |

|         | -                     |

| 6:<br>50<br>20 | 00                   | 90<br>500<br>96                              | 40<br>550<br>1.1                                   |

|----------------|----------------------|----------------------------------------------|----------------------------------------------------|

| 20             | 0                    |                                              |                                                    |

| 7              |                      | 96                                           | 1.1                                                |

| -              | 0.228                |                                              |                                                    |

|                | 0.220                |                                              | 0.0012                                             |

|                | 0.281                | 2.6                                          |                                                    |

| 1              | 0.509                |                                              |                                                    |

| 58             |                      | N/A                                          | N/A                                                |

| 50             |                      | 76                                           | 46.8                                               |

| 8.0            |                      | 12.3                                         | 7.5                                                |

| 0.0065         |                      | 0.4                                          | 0.012                                              |

| 1970           |                      | 504                                          | 6                                                  |

|                |                      |                                              |                                                    |

|                | 5<br>5<br>8.<br>0.00 | 1 0.509<br>58<br>50<br>8.0<br>0.0065<br>1970 | 50 0.509 58 N/A 50 76 8.0 12.3 0.0065 0.4 1970 504 |

\*Power - FoM =  $\frac{Power}{2 \cdot BW \cdot 2^{ENOB}}$  \*\*Area - FoM =  $\frac{Area}{2 \cdot BW \cdot 2^{ENOB}}$

Fig. 13 Comparison with other state-of-the-art ADCs.

#### 5. Effects of the Nonlinearity

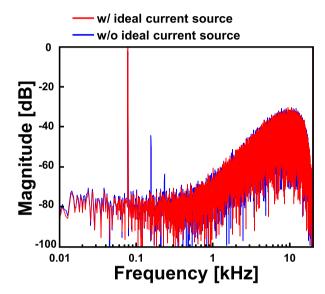

The resolution of the ADC is lower than that of [9] because of the nonlinearity characteristics. The reason of the nonlinearity is the current source in the proposed VTC. The timing diagram considering the drain-source current ( $I_{DS}$ ) characteristic is shown in Fig. 14. The gray line shows the timing diagram with the ideal current source, in which case  $I_{DS}$  stays at a fixed amount. The proposed VTC core, however, has nonlinearity because of its unstable current source.

Figure 15 shows the ADC output spectra, using the SPICE and MATLAB simulation result. The simulation without the ideal current source and the correction (section 3) has the harmonic noise because the VTC has nonlinearity. On the other hand, the characteristic of the VTC with the ideal current source achieves better linearity and the simulation result has no harmonic noise. To improve the proposed ADC, the  $I_{\rm DS}$  characteristic of the current source must be carefully redesigned.

Fig. 14 Timing diagram of the VTC core circuit with considering the effects of the  $I_{DS}$  characteristic.

Fig. 15 Simulation result with the ideal current source.

### 6. Conclusion

We described a 50-dB I/O-sized second-order ADC. The proposed architecture obviates analog circuits such as opamps and switched capacitors. The proposed VTC is especially affected by the  $I_{\rm DS}$  characteristic of the current source. By improving the current source, the proposed ADC would achieve higher resolution. The proposed ADC thereby maintains scalability with future advanced processes. As process technology advances, the ring oscillator frequency is expected to increase, which will be beneficial for the proposed ADC. A three-order or multiple-order ADC will be possible in our proposed ADC architecture.

## Acknowledgments

This development was performed by the authors for STARC as part of the Japanese Ministry of Economy, Trade and Industry sponsored "Silicon Implementation Support Program for Next Generation Semiconductor Circuit Architectures." The chip design was supported by the VLSI Design and Education Center (VDEC) of The University of Tokyo in collaboration with Synopsys Inc., Cadence Design Systems Inc., and Mentor Graphics Corp.

#### References

- S. Izumi, H. Noguchi, T. Takagi, K. Kugata, S. Soda, M. Yoshimoto, and H. Kawaguchi, "Data aggregation protocol for multiple sound sources acquisition with microphone array network," ICCCN, pp.1– 6, Aug. 2011.

- [2] S. O'Driscoll, K. V. Shenoy, and T. H. Meng, "Adaptive resolution ADC array for an implantable neural sensor," IEEE Trans. Biomed. Circuits Syst., vol.5, no.2, pp.120–130, Apr. 2011.

- [3] C. S. Taillefer and G. W. Roberts, "Delta-sigma A/D conversion via time-mode signal processing," IEEE Trans. Circuits Syst. I, vol.56, no.9, pp.1908–1920, Sept. 2009.

- [4] A. R. Macpherson, K. A. Townsend, and J. W. Haslett, "A 2.5 GS/s 3-bit time-based ADC in 90 nm CMOS," ISCAS, pp.9–12, May 2011.

- [5] A. R. Macpherson, J. W. Haslett, and L. Belostotski, "A 5 GS/s 4-bit time-based single-channel CMOS ADC for radio astronomy," CICC, pp.1–4, Sept. 2013.

- [6] S. Ok, J. Kim, G. Yoon, H. Chu, J. Oh, S. W. Kim, and C. Kim, "A DC-DC converter with a dual VCDL-based ADC and a self-calibrated DLL-based clock generator for an energy-aware EISC processor," CICC, pp.551–554, Sept. 2008.

- [7] G. Li, Y. M. Tousi, A. Hassibi, and E. Afshari, "Delay-line-based analog-to-digital converters," IEEE Trans. Circuits Syst. II, vol.56, no.6, pp.464–468, June 2009.

- [8] Y. M. Tousi and E. Afshari, "A miniature 2 mW 4 bit 1.2 GS/s delay-line-based ADC in 65 nm CMOS," IEEE J. Solid-State Circuits, vol.46, no.10, pp.2312–2325, Oct. 2011.

- [9] T. Konishi, K. Okuno, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "A second-order all-digital TDC with low-jitter frequency shift oscillators and dynamic flipflops," IEICE Trans. Electron., vol.E96-C, no.4, pp.546–552, Apr. 2013.

- [10] A. A. Abidi, "Phase noise and jitter in CMOS ring oscillators," IEEE JSSC, vol.41, no.8, pp.1803–1816, Aug. 2006.

- [11] S. L. Chen and M. D. Ker, "A new Schmitt trigger circuit in a 0.13μm 1/2.5-V CMOS process to receive 3.3-V input signals," IEEE Trans. Circuits. Syst., vol.52, no.7, pp.361–365, July 2005.

- [12] R. Gaggle, "Figure-of-merit comparison," in Delta-Sigma A/D-Converters, Springer Series in Advanced Microelectronics 39, eds. pp.129–135, Springer-Verlag, Berlin Heidelberg, 2013.

- [13] A. P. Perez, E. Bonizzoni, and F. Maloberti, "A 84 dB SndR 100 kHz bandwidth low-power single op-amp third-order  $\Delta\Sigma$  modulator consuming 140  $\mu$ w," ISSCC, pp.478–480, Feb. 2011.

- [14] M. Vadipour, C. Chen, A. Yazdi, M. Nariman, T. Li, P. Kilcoyne, and H. Darabi, "A 2.1 mW/3.2 mW delay-compensated GSM/WCDMA ΣΔ analog-digital converter," VLSI Symp., pp.180–181, June 2008.

- [15] S. Ouzounov, R. van Veldhoven, C. Bastiaansen, K. Vongehr, R. van Wegberg, G. Geelen, L. Breems, and A. van Roermund, "A 1.2 V, 121-mode CT ΔΣ modulator for wireless receivers in 90 nm CMOS," ISSCC, pp.242–600, Feb. 2007.

- [16] C. Y. Liou and C. C. Hsieh, "A 2.4-to-5.2 fJ/Conversion-step 10b 0.5-to-4 ms/s SAR ADC with charge average switching DAC in 90 nm CMOS," ISSCC, pp.280–281, Feb. 2013.

- [17] Y. Ke, P. Gao, J. Craninckx, G. Van der Plas, and G. Gielen, "A 2.8-to-8.5 mW GSM/Bluetooth/UMTS/DVB-H/WLAN fully reconfigurable CT ΔΣ with 200 kHz to 20 MHz BW for 4G radios in 90 nm digital CMOS," VLSI Symp., pp.153–154, June 2010.

- [18] A. Shikata, R. Sekimoto, T. Kuroda, and H. Ishikuro, "A 0.5 V 1.1 MS/sec 6.3 fJ/conversion-step SAR-ADC with tri-level comparator in 40 nm CMOS," VLSI Symp., pp.262–263, June 2011.

- [19] K. Okuno, T. Konishi, S. Izumi, M. Yoshimoto, and H. Kawaguchi, "An 8-bit I/O-Sized ADC with second-order TDC and MOM capacitor voltage-to-time converter," ICECS, pp.223–226, Dec. 2014.

Keisuke Okuno received a B.E. and M.Eng. degree in Computer and Systems Engineering from Kobe University, Hyogo, Japan in 2011 and 2013. Currently, he is a Ph.D. candidate at Kobe University. His current research interests include digital signal processing and adaptive filters. He is a member of the IEEE.

**Toshihiro Konishi** received B.Eng. and M.Eng. degrees in Computer Science and Systems Engineering from Kobe University, Hyogo, Japan in 2008 and 2010, respectively, where he is currently a Ph.D. candidate. He engages in low-power digitally controlled oscillator, analog-to-digital converters, time-to-digital converter designs, digitally assisted analog signal processing, and digital signal processing. He is a member of the IEEE, and IEICE.

Shintaro Izumi respectively received his B.Eng. and M.Eng. degrees in Computer Science and Systems Engineering from Kobe University, Hyogo, Japan, in 2007 and 2008. He received his Ph.D. degree in Engineering from Kobe University in 2011. He was a JSPS research fellow at Kobe University from 2009 to 2011. Since 2011, he has been an Assistant Professor in the Organization of Advanced Science and Technology at Kobe University. His current research interests include biomedical signal

processing, communication protocols, low-power VLSI design, and sensor networks. He is a member of the IEEE, IEICE, and IPSJ.

Masahiko Yoshimoto joined the LSI Laboratory, Mitsubishi Electric Corporation, Itami, Japan, in 1977. From 1978 to1983 he had been engaged in the design of NMOS and CMOS static RAM. Since 1984 he had been involved in the research and development of multimedia ULSI systems. He earned a Ph.D. degree in Electrical Engineering from Nagoya University, Nagoya, Japan in 1998. Since 2000, he had been a professor of Dept. of Electrical & Electronic System Engineering in Kanazawa Univer-

sity, Japan. Since 2004, he has been a professor of Dept. of Computer and Systems Engineering in Kobe University, Japan. His current activity is focused on the research and development of an ultra-low power multimedia and ubiquitous media VLSI systems and a dependable SRAM circuit. He holds on 70 registered patents. He has served on the program committee of the IEEE International Solid State Circuit Conference from 1991 to 1993. Also he served as Guest Editor for special issues on Low-Power System LSI, IP and Related Technologies of IEICE Transactions in 2004. He was a chair of IEEE SSCS (Solid State Circuits Society) Kansai Chapter from 2009 to 2010. He is also a chair of The IEICE Electronics Society Technical Committee on Integrated Circuits and Devices from 2011–2012. He received the R&D100 awards from the R&D magazine for the development of the DISP and the development of the realtime MPEG2 video encoder chipset in 1990 and 1996, respectively. He also received 21th TELECOM System Technology Award in 2006.

Hiroshi Kawaguchi received B.Eng. and M.Eng. degrees in electronic engineering from Chiba University, Chiba, Japan, in 1991 and 1993, respectively, and earned a Ph.D. degree in electronic engineering from The University of Tokyo, Tokyo, Japan, in 2006. He joined Konami Corporation, Kobe, Japan, in 1993, where he developed arcade entertainment systems. He moved to The Institute of Industrial Science, The University of Tokyo, as a Technical Associate in 1996, and was appointed as a Research

Associate in 2003. In 2005, he moved to Kobe University, Kobe, Japan. Since 2007, he has been an Associate Professor with The Department of Information Science at that university. He is also a Collaborative Researcher with The Institute of Industrial Science, The University of Tokyo. His current research interests include low-voltage SRAM, RF circuits, and ubiquitous sensor networks. Dr. Kawaguchi was a recipient of the IEEE ISSCC 2004 Takuo Sugano Outstanding Paper Award and the IEEE Kansai Section 2006 Gold Award. He has served as a Design and Implementation of Signal Processing Systems (DISPS) Technical Committee Member for IEEE Signal Processing Society, as a Program Committee Member for IEEE Custom Integrated Circuits Conference (CICC) and IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips), and as an Associate Editor of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and IPSJ Transactions on System LSI Design Methodology (TSLDM). He is a member of the IEEE, ACM, IEICE, and IPSJ.