ADAS Project

About the project

In the ADAS project, we are engaged in research and development of image recognition processor for advanced driving support system. We are improving and approaching from a wide field such as algorithm, architecture, digital circuit and design and develop LSI which detects real time object of high resolution video at low voltage.

Project research content

Object recognition is one of the element technologies necessary for autonomous driving and driving support. For applications to automobiles that are moving at high speed and related to human life, it is required to detect distant objects in real time, and demands for high definition video recognition technology are increasing. However, a huge amount of calculation is required for high resolution video processing. In addition, it is required to develop low power consumption device due to restrictions on battery capacity and thermal design. In the image recognition by software using GPGPU or high-performance CPU, there is also a problem of consuming a large amount of electric power even though enormous amount of calculation can be processed. Therefore, we aim to realize “low power consumption”, “high resolution” and “real time” by researching and developing dedicated processors.

Past research theme

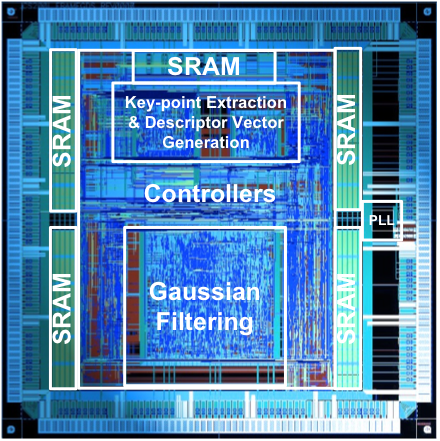

Low power consumption SIFT feature amount extraction processor for HDTV real time video recognition

SIFT feature is calculated based on the intensity gradient in the image and invariant to rotation and scale change. In SIFT, since only the part where an object is likely to be present becomes a target of object detection, efficient object detection becomes possible, and it is also applied to fields requiring real time properties such as object tracking.

In the processor we developed, we reduced the computational complexity by dividing the conventional two-dimensional smoothing into one-dimensional combinations, and we are reducing the power consumption by clock gating for each stage.

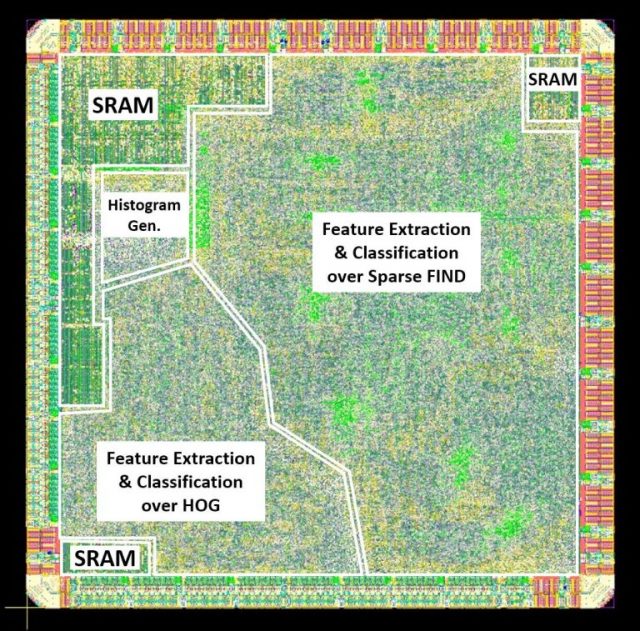

The below figure is a picture of the actual prototype chip.

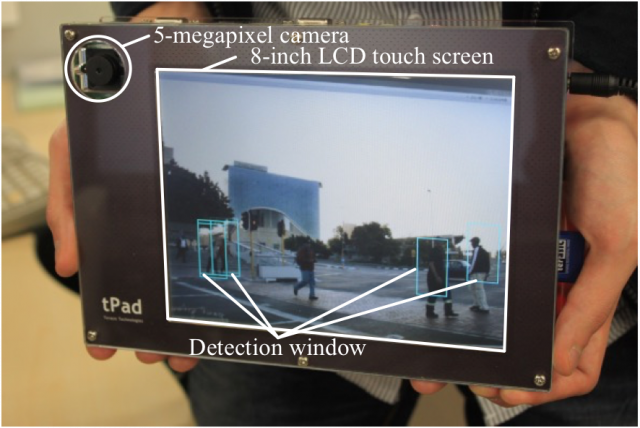

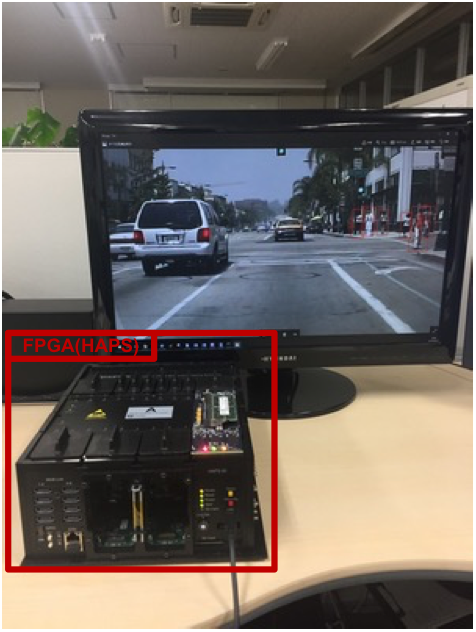

We also implement on the FPGA and build an object detection system.

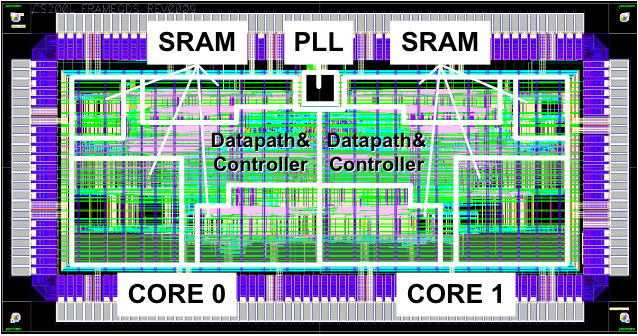

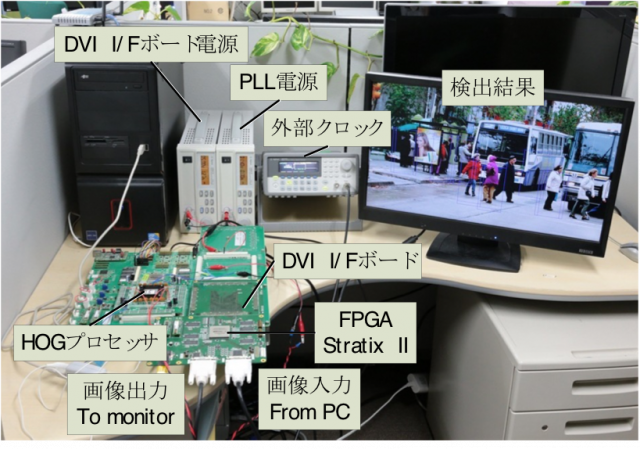

HDTV resolution compatible real time multi object detection processor using HOG features

HOG is a feature to obtain histogram of orientation of edge included in local region of image. Because it can capture a rough silhouette, this feature is robust against such as brightness and texture changes of an object. By taking this advantage , it is used for detection of various objects including person detection. For HOG, it is difficult to handle high resolution with software. We improved algorithms for hardware to realize the HOG processor. In addition, we propose an architecture in which computation modules are parallelized and pipelined for efficient computation.

In addition, we actually implemented the proposed processor in the FPGA, and also designed and developed the LSI chip. A typical CPU consumes about 50 W to 150 W, but the proposed processor consumes less than 200 mW of power. In this way, the place where processing can be done with high speed and power saving is the strength of the processor!

Multi-scale compatible HDTV resolution using Sparse FIND feature quantities @ 60 fps video recognition processor

Sparse FIND is a feature descriptor obtained by raising the brightness gradient histogram used for HOG feature quantity to a higher dimension and has higher detection accuracy than HOG and CoHOG used to detect objects in the automotive field in the past. In addition, we are targeting multi-scale object recognition in order to recognize objects of various sizes. However, the increase in the amount of computation due to higher dimensionality and randomness of RAM access, which video disturb high-speed processing of high-resolution. Therefore, we improved the algorithm and architecture to reduce variation in RAM access. We also built prototypes using FPGAs and designed LSI chips.

Strengths and future of the project

We are researching algorithms, architectures and circuits applied to image recognition processors and designing large-scale LSI chips. Also, we will build a demo system using not only chip design but also FPGA, so we can make the actually created processor visible.

We are planning to study real-time recognition processor using deep neural network in the future.

If you are interested in this research, who wanted to do this research, please feel free to visit professor Yoshimoto’s office.