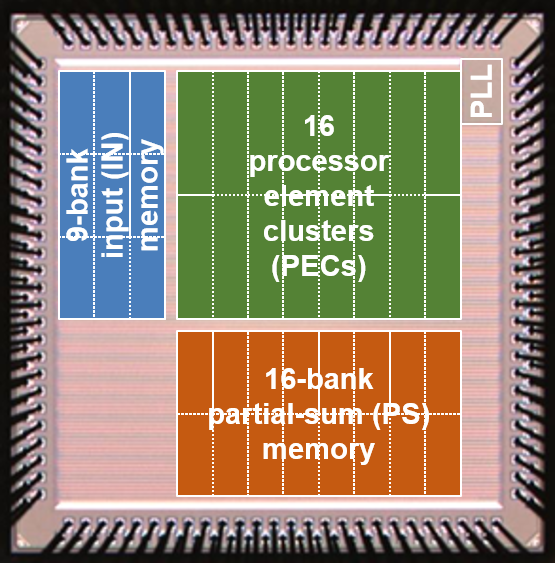

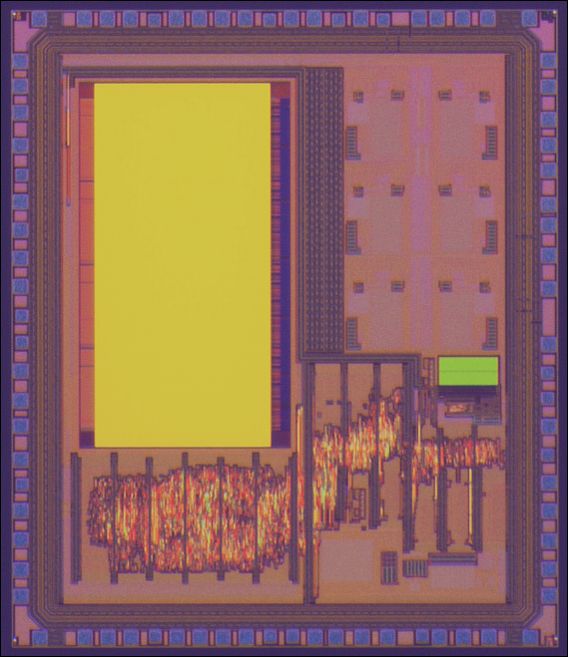

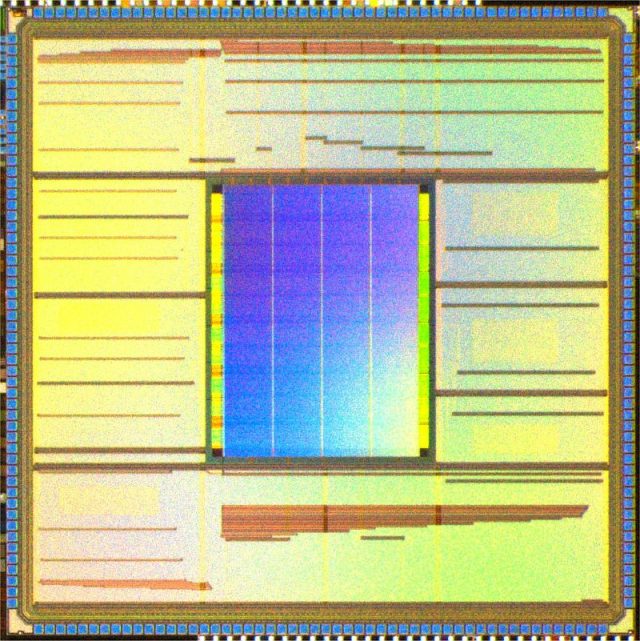

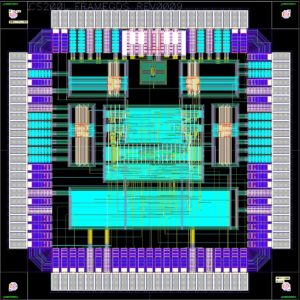

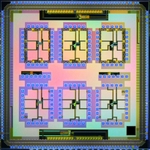

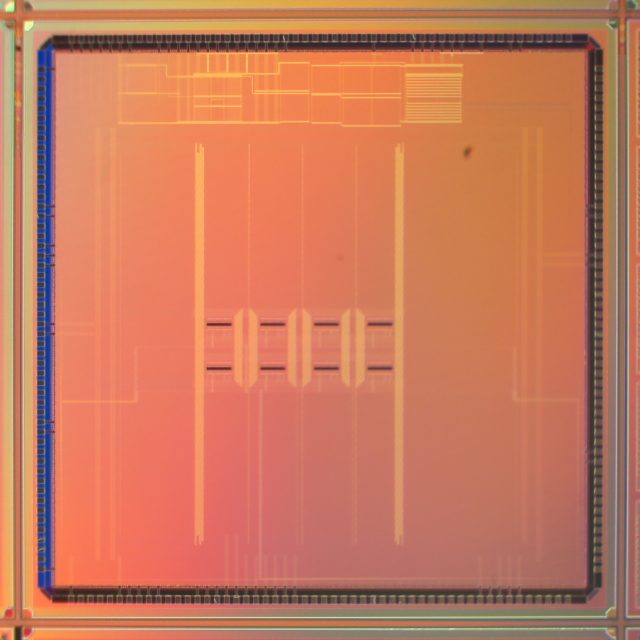

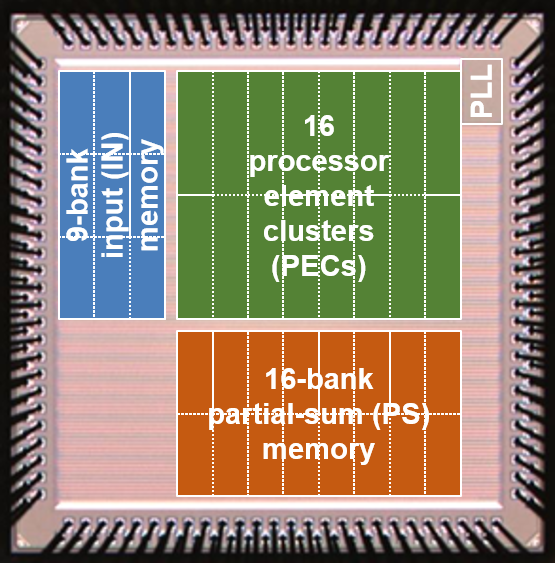

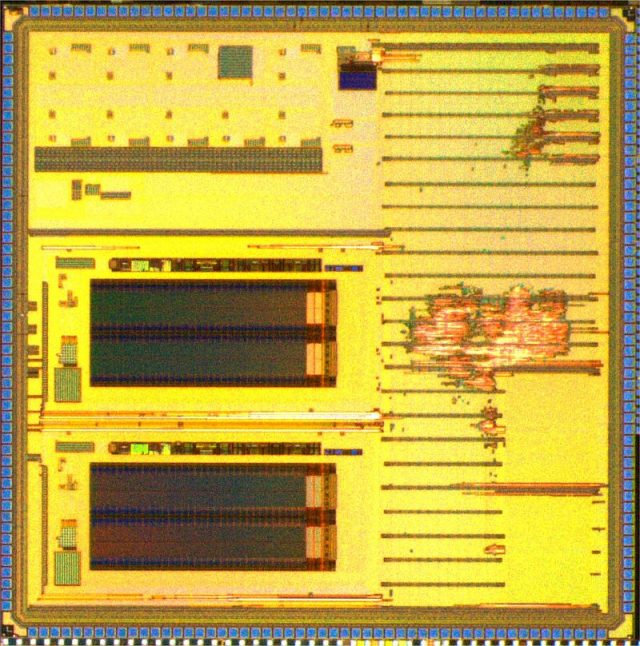

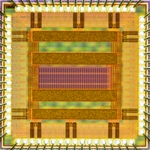

自動運転用 物体検出プロセッサ

- 40nm CMOSプロセス

- DVSプロジェクト,2019年

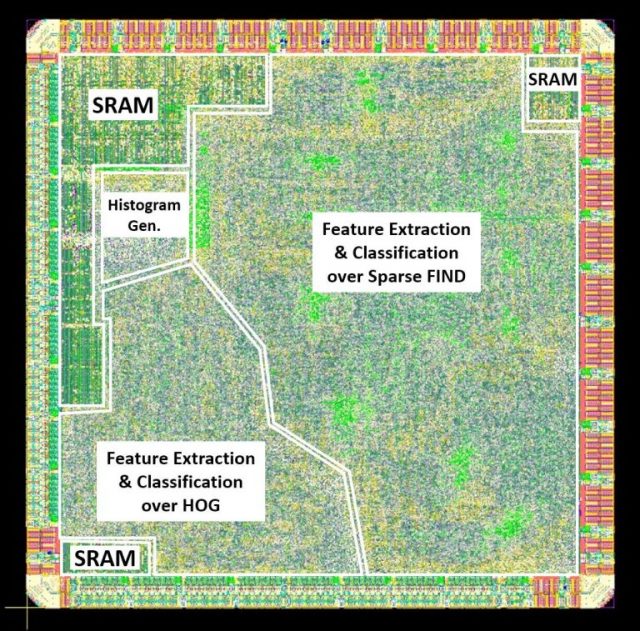

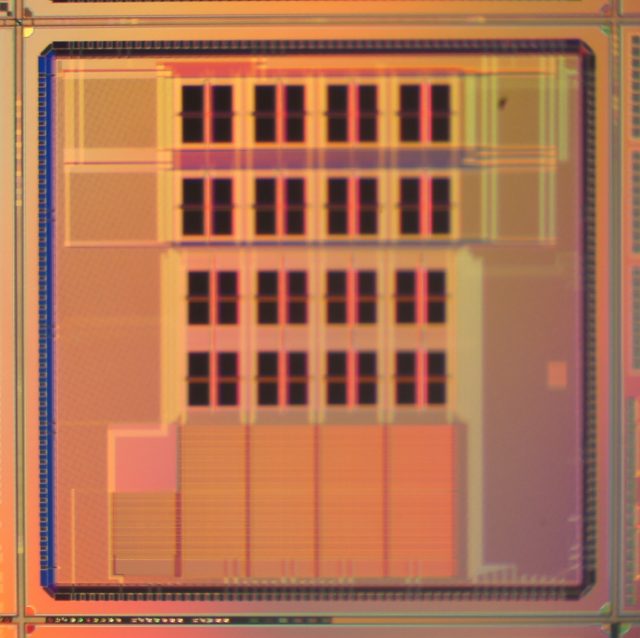

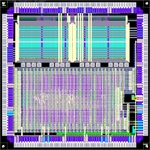

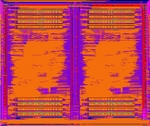

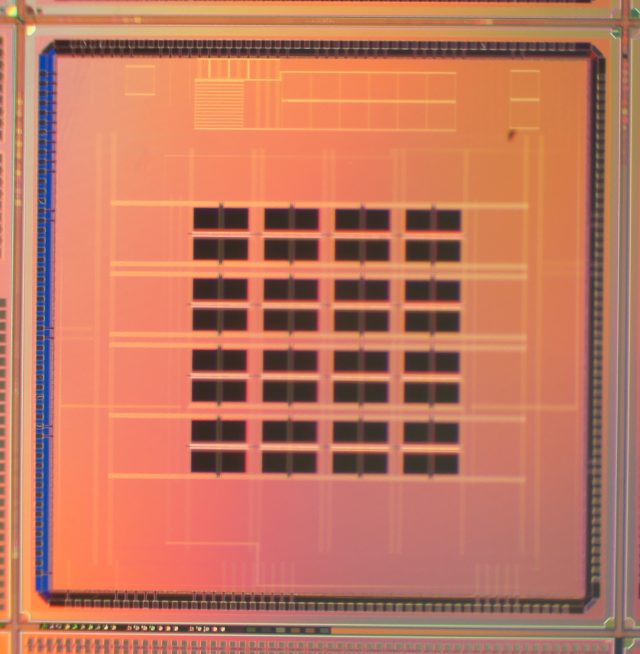

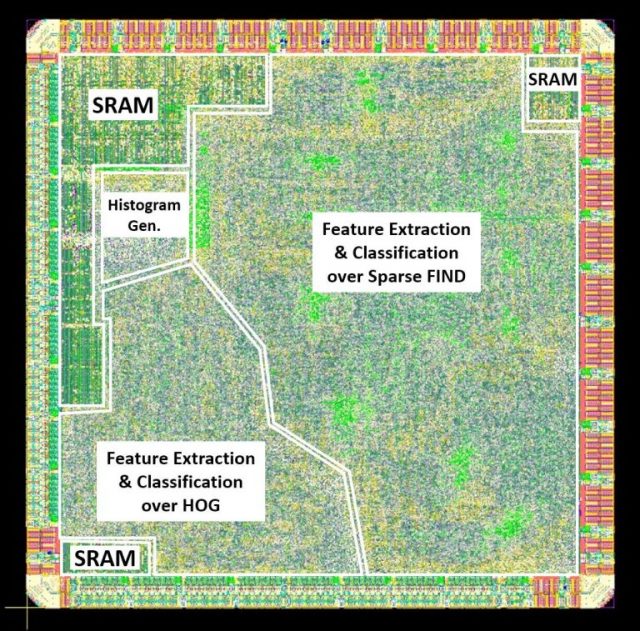

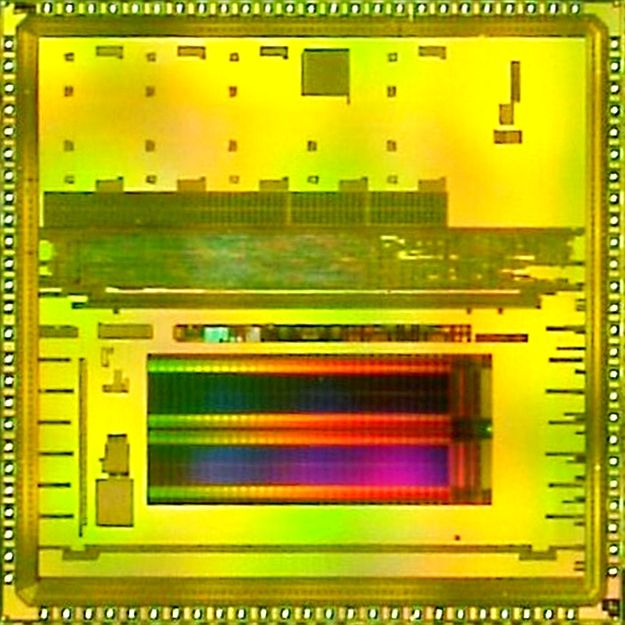

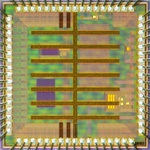

Sparse FINDを用いた超低消費電力物体認識プロセッサ

- 40nm CMOSプロセス

- DVSプロジェクト,2017年

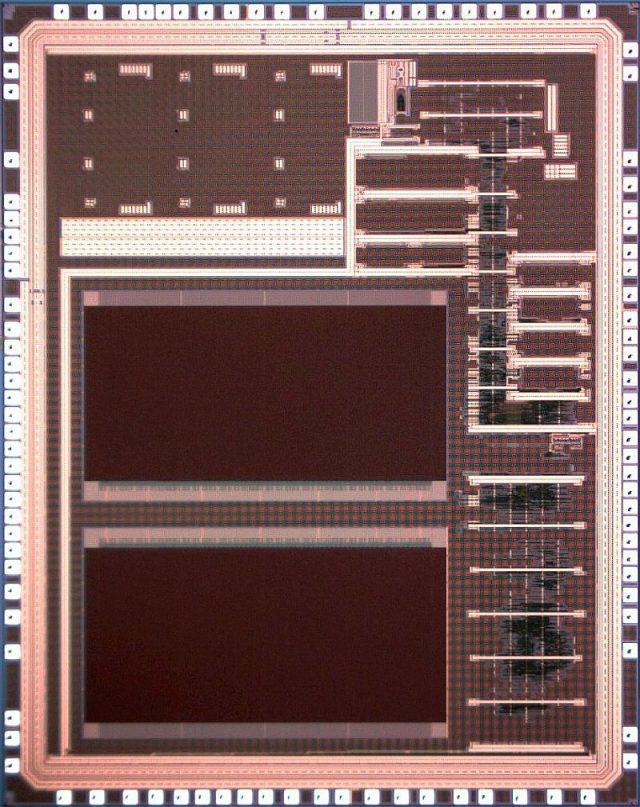

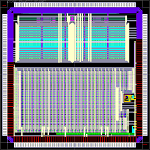

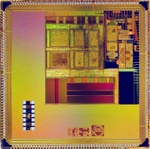

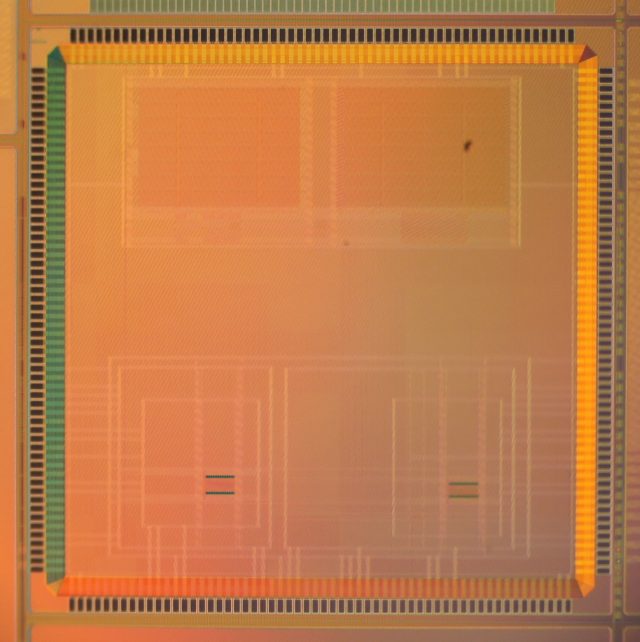

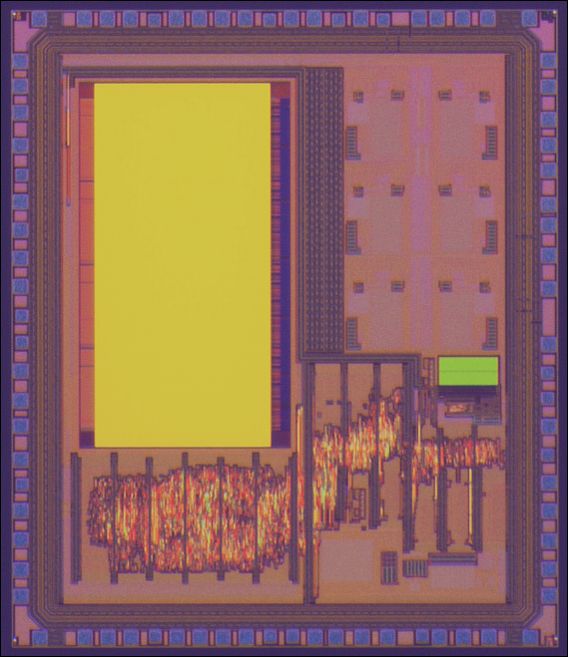

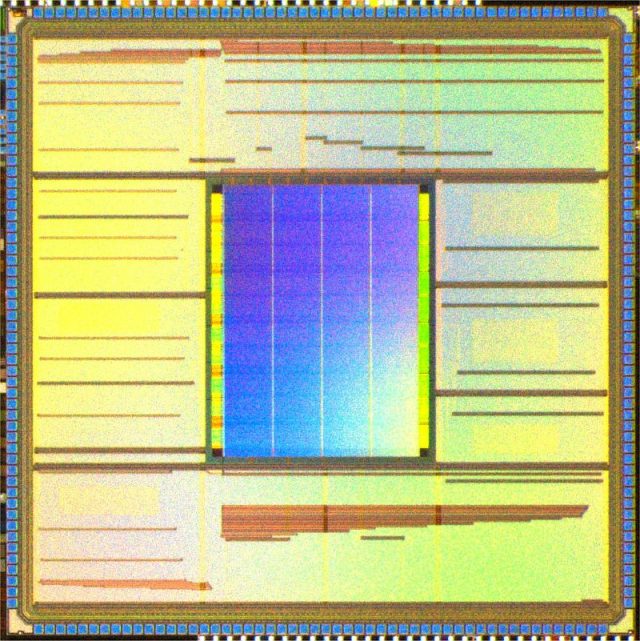

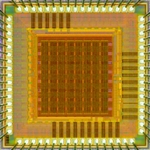

ノーマリーオフ生体センサSoC4

- 130nm CMOSプロセス

- WINEプロジェクト,2015年

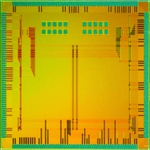

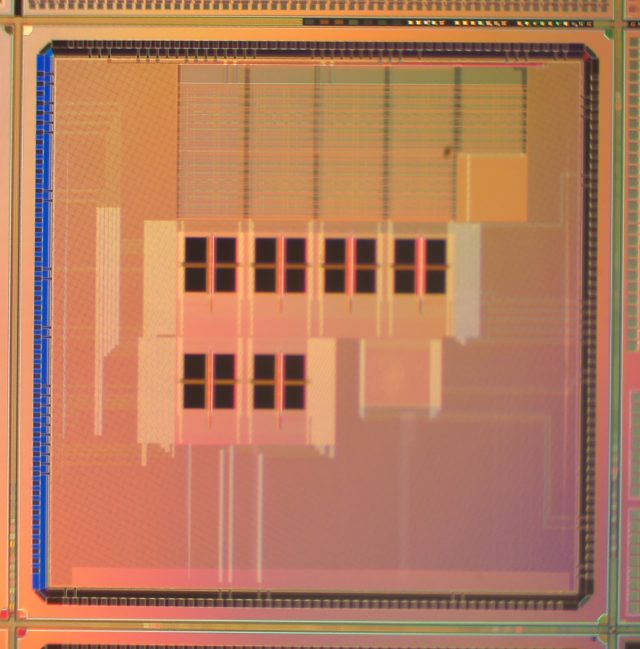

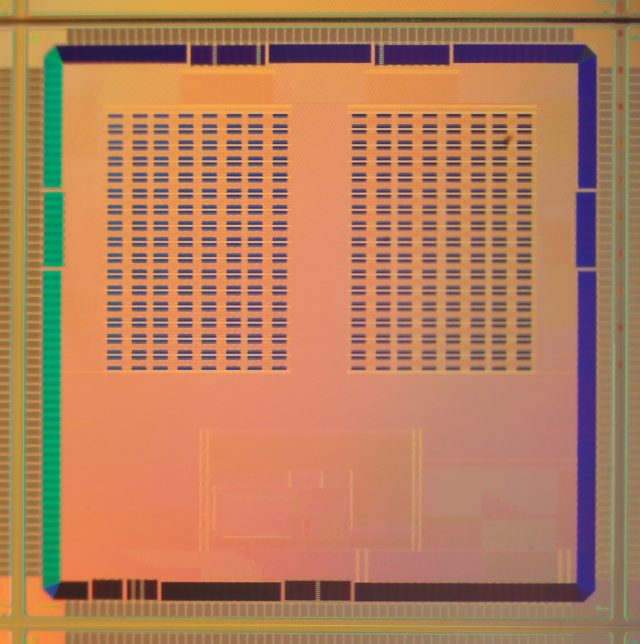

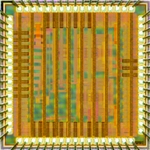

MRAM LPT7

- 65nm CMOSプロセス

- SRAMプロジェクト,2015年

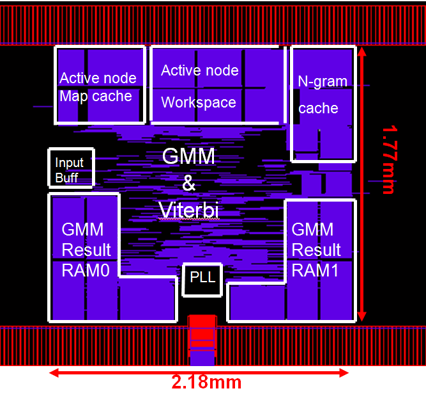

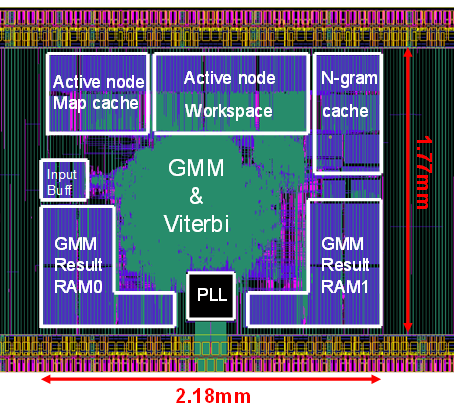

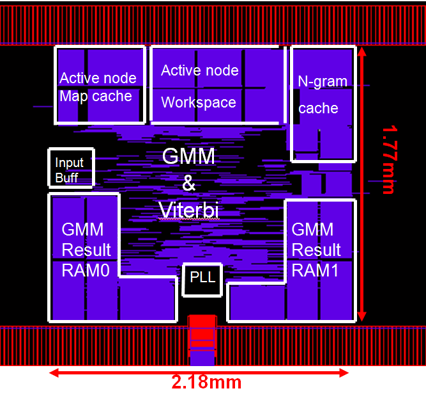

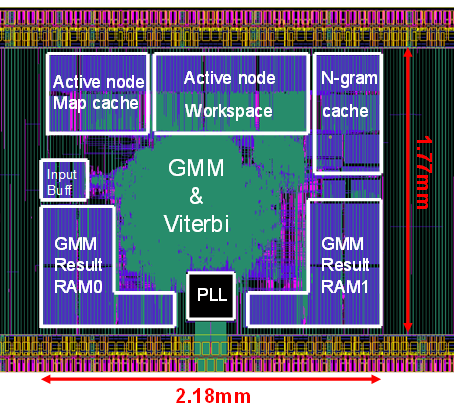

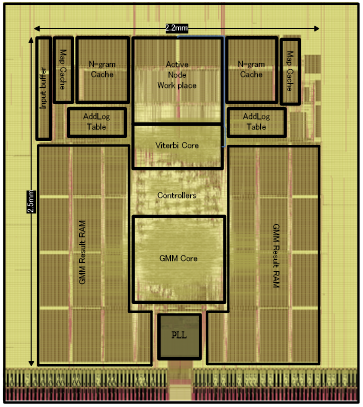

HMMを用いた6万語彙実時間連続音声認識プロセッサ3

- 40nm CMOSプロセス

- HYPERプロジェクト,2014年

MRAM LPT5-SC2

- 65nm CMOSプロセス

- SRAMプロジェクト,2014年

MRAM LPT5-SC1

- 65nm CMOSプロセス

- SRAMプロジェクト,2014年

MRAM LPT5S

- 65nm CMOSプロセス

- SRAMプロジェクト,2014年

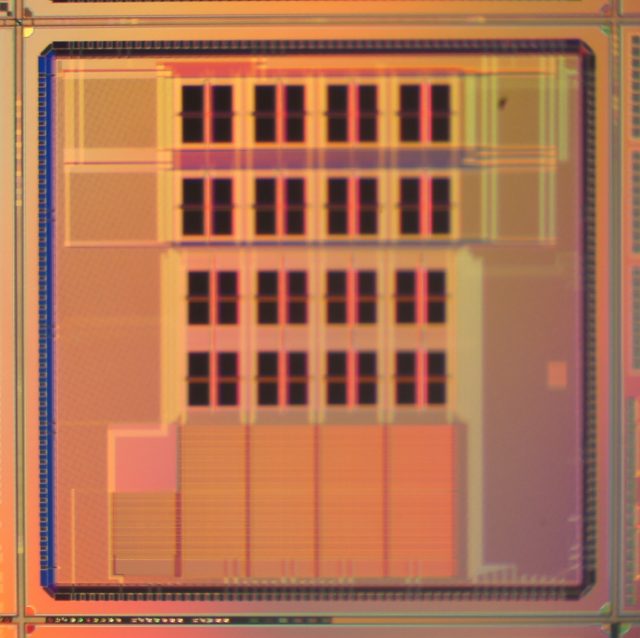

ノーマリーオフ生体センサSoC3

- 130nm CMOSプロセス

- WINEプロジェクト,2013年

MRAM LPT4

- 65nm CMOSプロセス

- SRAMプロジェクト,2013年

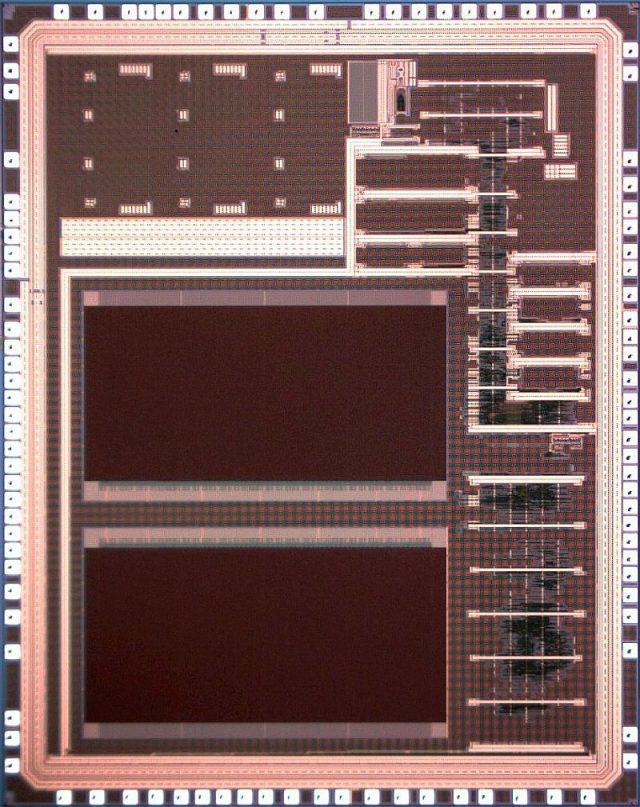

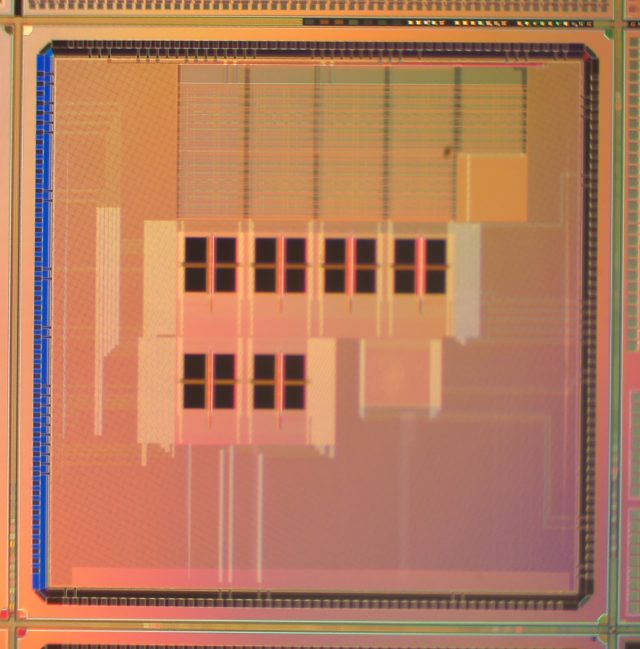

HOGを用いた実時間物体検出プロセッサ

- 65nm CMOSプロセス

- DVSプロジェクト,2012年

ノーマリーオフ生体センサSoC2

- 130nm CMOSプロセス

- WINEプロジェクト,2012年

ノーマリーオフ生体センサSoC1

- 130nm CMOSプロセス

- WINEプロジェクト,2012年

不揮発メモリTEG

- 130nm CMOSプロセス

- WINEプロジェクト,2012年

MRAM LPT2

- 65nm CMOSプロセス

- SRAMプロジェクト,2012年

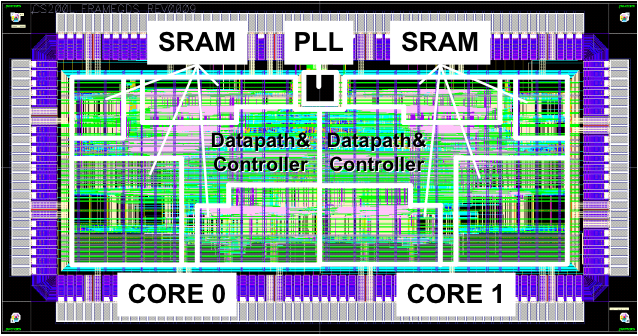

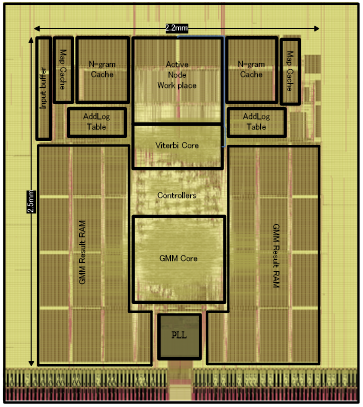

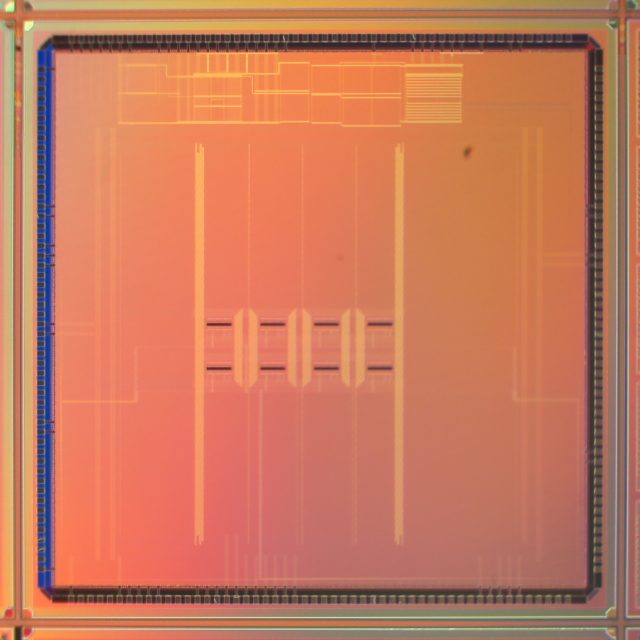

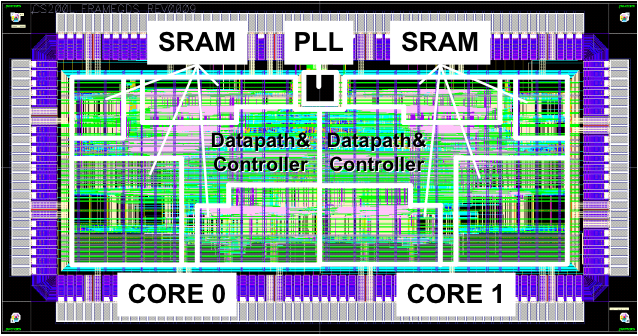

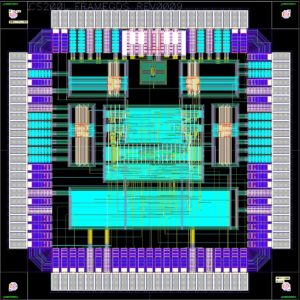

HMMを用いた6万語彙実時間連続音声認識プロセッサ2

- 40nm CMOSプロセス

- HYPERプロジェクト,2012年

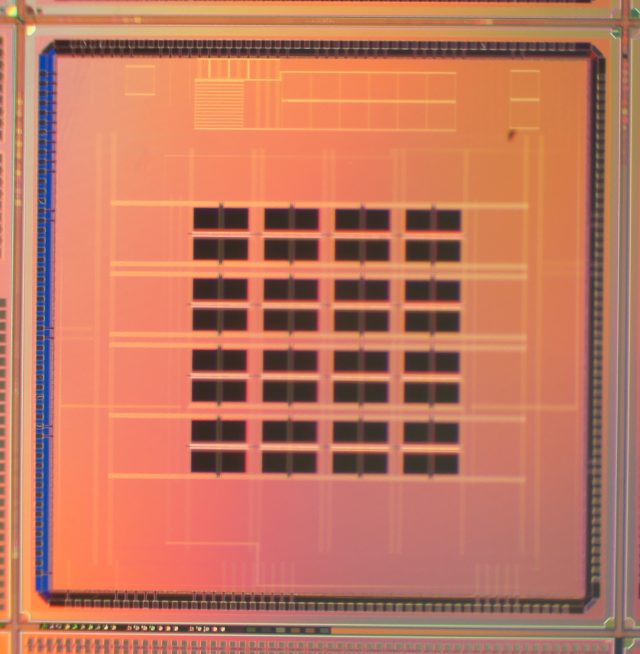

2.4倍速6万語彙実時間連続音声認識プロセッサ

- 40nm CMOSプロセス

- HYPERプロジェクト,2012年

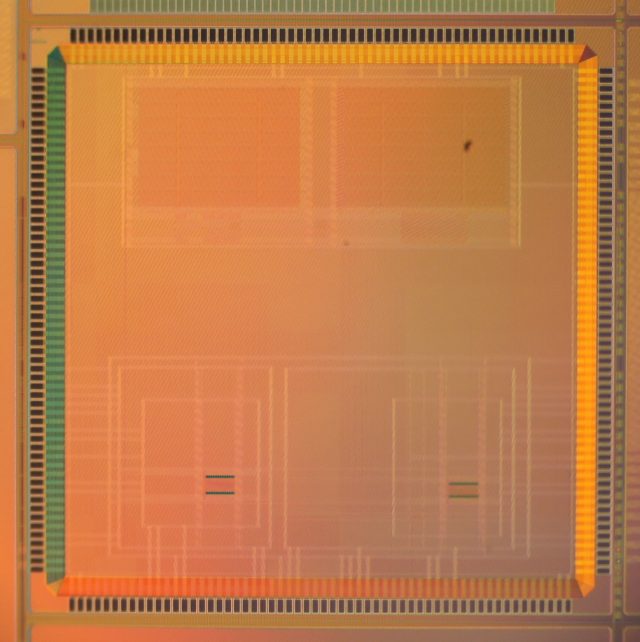

HMMを用いた6万語彙実時間音声認識のためのプロセッサ1

- 40nm CMOSプロセス

- HYPERプロジェクト,2011年

周波数制御型2次ΔΣTDC

- 65nm CMOSプロセス

- WINEプロジェクト,2011年

読出しビット線リミッタを備えた低消費電力 8T SRAM

- 40nm CMOSプロセス

- SRAMプロジェクト,2011年2月

640μm2 オペアンプレスAll Digital 2次MASH型ΔΣ A-D変換器

- 40nm CMOSプロセス

- WINEプロジェクト,2010年

ディペンダブルDigital Signal Processor

- 65nm CMOSプロセス

- HYPERプロジェクト,2010年12月

9T/18T SRAMとディペンダブルフリップフロップ

- 65nm CMOSプロセス

- HYPERプロジェクト,2010年2月

電圧・温度補償回路を用いたオープンループAll Digital PLL

- 65nm CMOSプロセス

- WINEプロジェクト,2010年11月

実時間動作の自律ロボット制御のための混合整数2次計画問題ソルバープロセッサ

- 40nm CMOSプロセス

- HYPERプロジェクト,2010年

差動WL 8T SRAMに向けたHalf-VDD生成回路TEG

- 40nm CMOSプロセス

- SRAMプロジェクト,2010年11月

BERモデル化のための1Mb 6T SRAM

- 65nm CMOSプロセス

- SRAMプロジェクト,2010年12月

0.5V 20.1pJ動作を実現する低消費電力ライトバック技術を備えた8T SRAM

- 40nm CMOSプロセス

- SRAMプロジェクト,2010年8月

ビットエラー耐性及びソフトエラー耐性を備えたFD-SOI 7T/14T SRAM

- 0.15um FD-SOIプロセス

- SRAMプロジェクト,2010年6月

ハーフセレクトセルのディスターブ耐性を高めた256k 8T SRAM

- 45nm CMOSプロセス

- SRAMプロジェクト,2009年

低電圧動作 45nm 128kb 10T SRAM

- 45nm CMOSプロセス

- SRAMプロジェクト,2007年7月

65nm 256kb 7T/14TディペンダブルSRAM

- 65nm CMOSプロセス

- SRAMプロジェクト,2007年10月

TEG(Multiphase VCOs@w=0.3um, 0.5um, 1.0um)とMultiphase Digital Controlled Oscillator

- 0.18um CMOSプロセス

- WINEプロジェクト,2008年1月

H.264/AVC Main-Profile対応・1/4画素精度動き検出プロセッサコア

- 90nm CMOSプロセス

- MEプロジェクト,2008年2月

再構成可能なベースバンド回路とハードウェアMACプロセッサを有する低消費電力 1-chip センサノードLSI

- 0.18um CMOSプロセス

- WINEプロジェクト,2008年6月

高速コピー機能を有する 65nm 1Mb 7T/14TディペンダブルSRAM

- 65nm CMOSプロセス

- SRAMプロジェクト,2008年11月

電源管理機能と時間同期機能を有する低消費電力 1-chip センサノードLSI

- 0.18um CMOSプロセス

- WINEプロジェクト,2009年2月

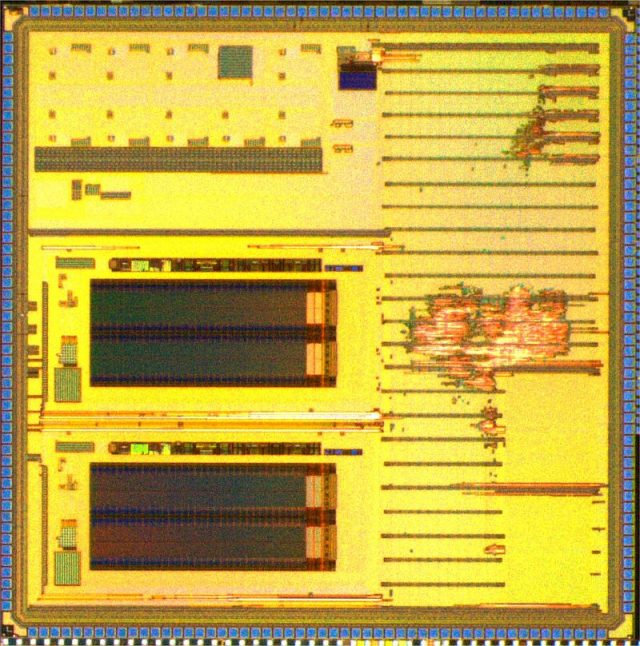

実時間HDTV動画像認識応用SIFT特徴量抽出プロセッサ

- 65nm CMOSプロセス

- HYPERプロジェクト,2009年

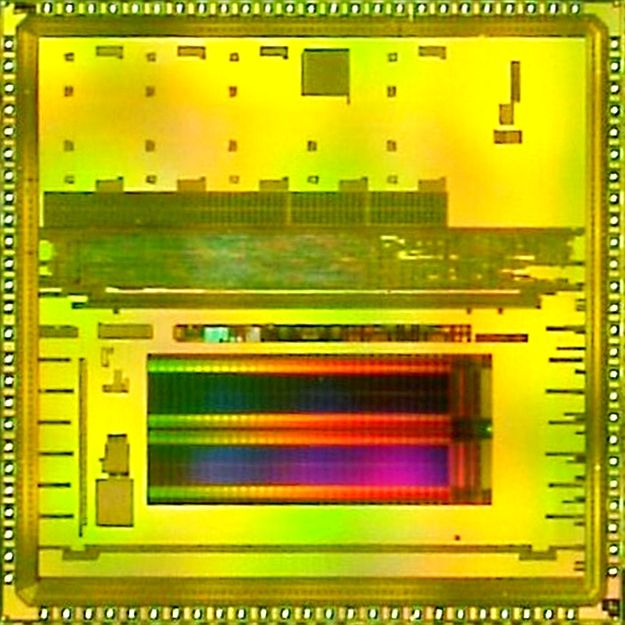

次世代知能ロボット制御のための混合整数2次計画問題(MIQP)ソルバープロセッサ

- 65nm CMOSプロセス

- HYPERプロジェクト,2009年

オペアンプレス・キャパシタレスΔ-Σ型ADC

- 65nm CMOSプロセス

- WINEプロジェクト,2009年

低電力20相出力発振回路

- 65nm CMOSプロセス

- WINEプロジェクト,2009年

基盤バイアス制御回路を用いた7T/14TディペンダブルSRAM

- 0.15um FD-SOIプロセス

- SRAMプロジェクト,2009年6月

BIST機能を有する65nm 512Kb 7T/14TディペンダブルSRAM

- 65nm CMOSプロセス

- SRAMプロジェクト,2009年

ソフトエラー耐性を高めた65nm 512Kb 6T SRAM

- 65nm CMOSプロセス

- SRAMプロジェクト,2009年

ビット線充放電電力を削減する90-nm 64-Kbit 10TSRAM

- 90nm CMOSプロセス

- SRAMプロジェクト,2006年11月

フィードバック型アルゴリズムで動的に電圧と周波数を制御するHD対応H.264デコーダLSI

- 0.15um SOIプロセス

- FAプロジェクト,2006年11月

TEG(FSKフロントエンド,BSAMP,SAW,FBAR発振回路)

- 0.15um SOIプロセス

- WINEプロジェクト,2006年10月

I-MAC対応キャリアセンス機能を有するセンサノードLSI

- 0.15um SOIプロセス

- WINEプロジェクト,2006年10月

基板バイアス制御を用いた0.42V動作486kb FD-SOI SRAM

- 0.15um SOIプロセス

- SRAMプロジェクト,2006年10月

動画像処理応用低消費電力2-port SRAM

- 90nm CMOSプロセス

- SRAMプロジェクト,2006年7月

TEG(DCO,水晶発振回路,トランジスタ,温度補償バイアス回路)

- 0.15um SOIプロセス

- WINEプロジェクト,2006年5月

800-μW H.264Baseline-Profile対応�動き検出プロセッサIP

- 0.13um CMOSプロセス

- MEプロジェクト,2006年1月

動的電圧制御環境下における低電圧動作90-nm 1Mbit SRAM

- 90nm CMOSプロセス

- SRAMプロジェクト,2005年10月

TEG(900MHz帯向けVCO,PA,LNA,Mixer)

- 0.15um SOIプロセス

- WINEプロジェクト,2005年9月

動的電圧制御環境下における低電圧動作90-nm 64-Kbit SRAM

- 90nm CMOSプロセス

- SRAMプロジェクト,2005年5月

ASK送受信機

- 90nm CMOSプロセス

- ME,WINEプロジェクト,2005年5月

動的電圧制御 超低消費電力 90nm 512Kbit SRAM

- 90nm CMOSプロセス

- FAプロジェクト,2004年12月

ALUおよびトランジスタTEG

- 90nm CMOSプロセス

- FAプロジェクト,2004年12月

95mW MPEG2 MP@HL 動き検出プロセッサコアIP

- 0.18um CMOSプロセス

- MEプロジェクト,2004年6月

400μW MPEG4 動き検出プロセッサコアIP

- 0.18um CMOSプロセス

- MEプロジェクト,2003年1月

MPEG2 HDTV対応動き検出プロセッサコアIP

- 0.13um CMOSプロセス

- MEプロジェクト,2001年10月

MPEG2 HDTV対応動き検出プロセッサコアIP

- 0.13um CMOSプロセス

- MEプロジェクト,2001年10月